# X20CS2770

## 1 General information

In addition to the standard I/O, complex devices often need to be connected. The X20 CS communication modules are intended precisely for cases like this. As normal X20 electronics modules, they can be placed anywhere on the remote backplane.

- · 2 CAN bus interfaces for serial, remote connection of complex devices to the X20 system

- · Integrated terminating resistors

## 2 Order data

| Order number | Short description                                                                                               | Figure     |

|--------------|-----------------------------------------------------------------------------------------------------------------|------------|

|              | X20 electronics module communication                                                                            |            |

| X20CS2770    | X20 interface module, 2 CAN bus interfaces, max. 1 Mbit/s, object buffer in the transmit and receive directions | 33         |

|              | Required accessories                                                                                            | S          |

|              | Bus modules                                                                                                     | 2 S 2 1 12 |

| X20BM11      | X20 bus module, 24 VDC keyed, internal I/O supply continuous                                                    | X20        |

| X20BM15      | X20 bus module, with node number switch, 24 VDC keyed, internal I/O power supply connected through              |            |

|              | Terminal blocks                                                                                                 |            |

| X20TB12      | X20 terminal block, 12-pin, 24 VDC keyed                                                                        |            |

Table 1: X20CS2770 - Order data

# 3 Technical data

| Order number                                                     | X20CS2770                                                                                            |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Short description                                                |                                                                                                      |

| Communication module                                             | 2x CAN bus                                                                                           |

| General information                                              |                                                                                                      |

| B&R ID code                                                      | 0xA009                                                                                               |

| Status indicators                                                | Data transfer, terminating resistor, operating state, module status                                  |

| Diagnostics                                                      |                                                                                                      |

| Module run/error                                                 | Yes, using LED status indicator and software                                                         |

| Data transfer                                                    | Yes, using LED status indicator                                                                      |

| Terminating resistor                                             | Yes, using LED status indicator                                                                      |

| Power consumption                                                |                                                                                                      |

| Bus                                                              | 0.01 W                                                                                               |

| Internal I/O                                                     | 0.55 W (Rev. ≤D0 1.5 W)                                                                              |

| Additional power dissipation caused by actuators (resistive) [W] | -                                                                                                    |

| Certifications                                                   |                                                                                                      |

| CE                                                               | Yes                                                                                                  |

| ATEX                                                             | Zone 2, II 3G Ex nA nC IIA T5 Gc<br>IP20, Ta (see X20 user's manual)<br>FTZÚ 09 ATEX 0083X           |

| UL                                                               | cULus E115267<br>Industrial control equipment                                                        |

| HazLoc                                                           | cCSAus 244665 Process control equipment for hazardous locations Class I, Division 2, Groups ABCD, T5 |

| EAC                                                              | Yes                                                                                                  |

| KC                                                               | Yes                                                                                                  |

| Interfaces                                                       |                                                                                                      |

| Interface IF1                                                    |                                                                                                      |

| Signal                                                           | CAN bus                                                                                              |

| Variant                                                          | Connection made using 12-pin terminal block X20TB12                                                  |

| Max. distance                                                    | 1000 m                                                                                               |

| Transfer rate                                                    | Max. 1 Mbit/s                                                                                        |

| Terminating resistor                                             | Integrated in module                                                                                 |

| Controller                                                       | SJA 1000                                                                                             |

| Interface IF2                                                    |                                                                                                      |

| Signal                                                           | CAN bus                                                                                              |

| Variant                                                          | Connection made using 12-pin terminal block X20TB12                                                  |

| Max. distance                                                    | 1000 m                                                                                               |

| Transfer rate                                                    | Max. 1 Mbit/s                                                                                        |

| Terminating resistor                                             | Integrated in module                                                                                 |

| Controller                                                       | SJA 1000                                                                                             |

| Electrical properties                                            | 33A 1000                                                                                             |

| Electrical properties  Electrical isolation                      | CAN (IF1, IF2) isolated from bus and I/O power supply                                                |

|                                                                  | CAN (IF1, IF2) isolated from each other                                                              |

| Operating conditions                                             |                                                                                                      |

| Mounting orientation                                             | V.                                                                                                   |

| Horizontal                                                       | Yes                                                                                                  |

| Vertical                                                         | Yes                                                                                                  |

| Installation elevation above sea level                           |                                                                                                      |

| 0 to 2000 m                                                      | No limitation                                                                                        |

| >2000 m                                                          | Reduction of ambient temperature by 0.5°C per 100 m                                                  |

| Degree of protection per EN 60529                                | IP20                                                                                                 |

| Ambient conditions                                               |                                                                                                      |

| Temperature                                                      |                                                                                                      |

| Operation                                                        |                                                                                                      |

| Horizontal mounting orientation                                  | -25 to 60°C                                                                                          |

| Vertical mounting orientation                                    | -25 to 50°C                                                                                          |

| Derating                                                         | See section "Derating".                                                                              |

| Storage                                                          | -40 to 85°C                                                                                          |

| Transport                                                        | -40 to 85°C                                                                                          |

| Relative humidity                                                |                                                                                                      |

| Operation                                                        | 5 to 95%, non-condensing                                                                             |

| Storage                                                          | 5 to 95%, non-condensing                                                                             |

| Transport                                                        | 5 to 95%, non-condensing                                                                             |

| Mechanical properties                                            |                                                                                                      |

| Note                                                             | Order 1x terminal block X20TB12 separately.<br>Order 1x bus module X20BM11 separately.               |

| Pitch                                                            | 12.5 <sup>+0.2</sup> mm                                                                              |

|                                                                  | 1-15                                                                                                 |

Table 2: X20CS2770 - Technical data

## 4 LED status indicators

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" in the X20 system user's manual.

| Figure   | LED   | Color          | Status       | Description                                                                        |

|----------|-------|----------------|--------------|------------------------------------------------------------------------------------|

|          | r     | Green          | Off          | No power to module                                                                 |

|          |       |                | Single flash | RESET mode                                                                         |

|          |       |                | Double flash | BOOT mode (during firmware update) <sup>1)</sup>                                   |

|          |       |                | Blinking     | PREOPERATIONAL mode                                                                |

|          |       |                | On           | RUN mode                                                                           |

| o re     |       |                | Off          | No power to module or everything OK                                                |

| Tx1Rx1   |       |                | Single flash | I/O error occurred                                                                 |

| N Tx2Rx2 |       |                |              | CAN bus: Warning, passive or off                                                   |

| S T1 T2  |       |                |              | Buffer overflow                                                                    |

| X20      |       |                | On           | Error or reset status                                                              |

|          | e + r | Red on / Green | single flash | Invalid firmware                                                                   |

| Tx1/2 Ye |       | Yellow         | On           | The module is sending data via the CAN bus interface IF1/IF2                       |

|          | Rx1/2 | Yellow         | On           | The module is receiving data via the CAN bus interface IF1/IF2                     |

|          | T1/2  | Yellow         | On           | The integrated terminating resistor for the CAN bus interface IF1/IF2 is turned on |

<sup>1)</sup> Depending on the configuration, a firmware update can take up to several minutes.

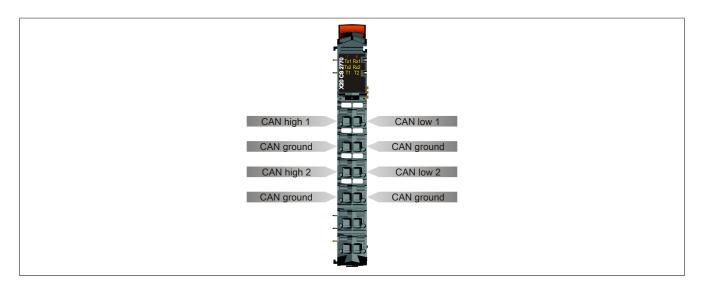

# **5 Pinout**

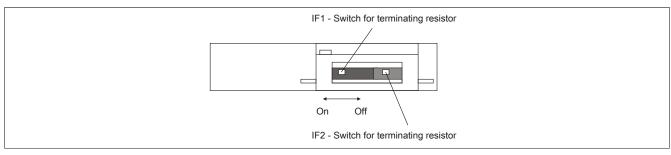

## **6 Terminating resistors**

Two terminating resistors are integrated in the communication module. The respective resistor can be turned on and off with a switch on the bottom of the housing. An active terminating resistor is indicated by the "T1" or "T2" LED.

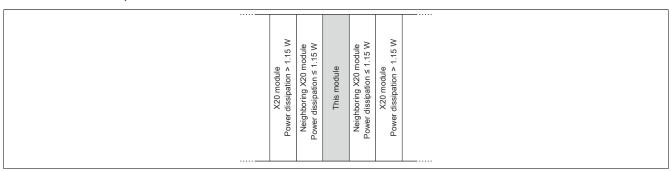

# 7 Derating

### Up to hardware revision ≤D0

There is no derating when operated below 55°C.

During operation over 55°C, the power dissipation of the modules to the left and right of this module is not permitted to exceed 1.15 W!

For an example of calculating the power dissipation of I/O modules, see section "Mechanical and electrical configuration - Power dissipation of I/O modules" in the X20 user's manual.

## Hardware revision >D0 and later

No derating

# 8 Usage after the X20IF1091-1

If this module is operated after X2X Link module X20IF1091-1, delays may occur during the Flatstream transfer. For detailed information, see section "Data transfer on the Flatstream" in X20IF1091-1.

## 9 Register description

### 9.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X20 system user's manual.

#### 9.2 Function model 0 - Flat

In the "Flat" function model, CAN information is transferred via cyclic input and output registers. All data for a CAN object (8 CAN data bytes, identifier, status, etc.) is accessible as individual data points (see also "CAN object" on page 9).

To transmit a CAN object, the CAN identifier, the CAN data (max. 8 bytes) and the number of bytes to be transmitted must be written to the cyclic I/O data points. Then, "TX0[x]Count" is increased to send the transmission. The data is held in the module's internal buffer (max. 18 objects) and transmitted over the CAN network at the next available opportunity.

Receiving information from the CAN network uses the same algorithm. The module saves the CAN messages in its internal buffer along with the respective identifiers. Then the CAN identifier, the CAN data (max. 8 bytes) and the number of bytes to be processed are written to the cyclic I/O data points. RX0[x]Count tells the application how much new data must be taken from these input data points.

### Information:

• Libraries "ArCAN" and "CAN\_Lib" cannot be used.

| Register         | Name                           | Data type | Read   |            | Write  |            |

|------------------|--------------------------------|-----------|--------|------------|--------|------------|

|                  |                                |           | Cyclic | Non-cyclic | Cyclic | Non-cyclic |

| Interface - Conf |                                |           |        |            |        |            |

| 257              | Config01Baudrate               | USINT     |        |            |        | •          |

| 259              | Config01SJW                    | USINT     |        |            |        | •          |

| 261              | Config01SPO                    | USINT     |        |            |        | •          |

| 266              | Config01TXtrigger              | UINT      |        |            |        | •          |

| 673              | Cfo_FIFOTXlimit01              | USINT     |        |            |        | •          |

| 677              | Cfo_TXRXinfoFlags01            | USINT     |        |            |        | •          |

| 769              | Config02Baudrate               | USINT     |        |            |        | •          |

| 771              | Config02SJW                    | USINT     |        |            |        | •          |

| 773              | Config02SPO                    | USINT     |        |            |        | •          |

| 778              | Config02TXtrigger              | UINT      |        |            |        | •          |

| 1185             | Cfo_FIFOTXlimit02              | USINT     |        |            |        | •          |

| 1189             | Cfo_TXRXinfoFlags02            | USINT     |        |            |        | •          |

| Interface - Com  | munication                     |           |        |            |        |            |

| 641              | TX01Count                      | USINT     |        |            | •      |            |

| 513              | TX01CountReadBack              | USINT     | •      |            |        |            |

| 515              | RX01Count                      | USINT     | •      |            |        |            |

| 1153             | TX02Count                      | USINT     |        |            | •      |            |

| 1025             | TX02CountReadBack              | USINT     | •      |            |        |            |

| 1027             | RX02Count                      | USINT     | •      |            |        |            |

| Transmit buffer  | IF1                            |           |        |            |        |            |

| 645              | TX01DataSize                   | USINT     |        |            | •      |            |

| 652              | TX01Ident                      | UDINT     |        |            | •      |            |

| Index * 2 + 657  | TX01DataByte0 to TX01DataByte7 | USINT     |        |            | •      |            |

| Index * 4 + 658  | TX01DataWord0 to TX01DataWord3 | UINT      |        |            | •      |            |

| Index * 8 + 660  | TX01DataLong0 to TX01DataLong1 | UDINT     |        |            | •      |            |

| Receive buffer I | F1                             |           |        |            |        |            |

| 517              | RX01DataSize                   | USINT     | •      |            |        |            |

| 524              | RX01Ident                      | UDINT     | •      |            |        |            |

| Index * 2 + 529  | 3                              | USINT     | •      |            |        |            |

| Index * 4 + 530  | RX01DataWord0 to RX01DataWord3 | UINT      | •      |            |        |            |

| Index * 8 + 532  | RX01DataLong0 to RX01DataLong1 | UDINT     | •      |            |        |            |

| Transmit buffer  | IF2                            |           |        |            |        |            |

| 1157             | TX02DataSize                   | USINT     |        |            | •      |            |

| 1164             | TX02Ident                      | UDINT     |        |            | •      |            |

| Index * 2 + 1170 | TX02DataByte0 to TX02DataByte7 | USINT     |        |            | •      |            |

| Index * 4 + 658  | TX02DataWord0 to TX02DataWord3 | UINT      |        |            | •      |            |

| Index * 8 + 1172 | TX02DataLong0 to TX02DataLong1 | UDINT     |        |            | •      |            |

| Receive buffer I | F2                             |           |        |            |        |            |

| 1029             | RX02DataSize                   | USINT     | •      |            |        |            |

| Register         | Name                           | Data type | Read   |            | W      | Write      |  |

|------------------|--------------------------------|-----------|--------|------------|--------|------------|--|

|                  |                                |           | Cyclic | Non-cyclic | Cyclic | Non-cyclic |  |

| 1036             | RX02Ident                      | UDINT     | •      |            |        |            |  |

| Index * 2 + 1041 | RX02DataByte0 to RX02DataByte7 | USINT     | •      |            |        |            |  |

| Index * 4 + 1042 | RX02DataWord0 to RX02DataWord3 | UINT      | •      |            |        |            |  |

| Index * 8 + 1044 | RX02DataLong0 to RX02DataLong1 | UDINT     | •      |            |        |            |  |

## 9.3 Function model 2 - Stream and Function model 254 - Cyclic stream

Function models "Stream" and "Cyclic stream" use a module-specific driver of the CPU's operating system. The interface can be controlled using libraries "ArCAN" and "CAN\_Lib" and reconfigured at runtime.

#### **Function model - Stream**

In function model "Stream", the CPU communicates with the module acyclically. The interface is relatively convenient, but the timing is very imprecise.

### Function model - Cyclic stream

Function model "Cyclic stream" was implemented later. From the application's point of view, there is no difference between function models "Stream" and "Cyclic stream". Internally, however, the cyclic I/O registers are used to ensure that communication follows deterministic timing.

## Information:

- In order to use function models "Stream" and "Cyclic stream", you must be using B&R controllers of type "SG4".

- These function models can only be used in X2X Link and POWERLINK networks.

| Register       | Name                     | Data type | R      | ead     | W      | Write   |  |

|----------------|--------------------------|-----------|--------|---------|--------|---------|--|

|                |                          |           | Cyclic | Acyclic | Cyclic | Acyclic |  |

| Module - Cor   | figuration               |           |        |         |        |         |  |

| -              | AsynSize                 | -         |        |         |        |         |  |

| Interface - Co | onfiguration             |           |        |         |        |         |  |

| 6273           | CfO_ErrorID0007          | USINT     |        |         |        | •       |  |

| Interface - Co | mmunication              |           |        |         |        |         |  |

| 6145           | CAN error status         | USINT     | •      |         |        |         |  |

|                | CANIF1warning            | Bit 0     |        |         |        |         |  |

|                | CANIF1passive            | Bit 1     |        |         |        |         |  |

|                | CANIF1busoff             | Bit 2     |        |         |        |         |  |

|                | CANIF1RXoverrun          | Bit 3     |        |         |        |         |  |

|                | CANIF2warning            | Bit 4     |        |         |        |         |  |

|                | CANIF2passive            | Bit 5     |        |         |        |         |  |

|                | CANIF2busoff             | Bit 6     |        |         |        |         |  |

|                | CANIF2RXoverrun          | Bit 7     |        |         |        |         |  |

| 6209           | CAN error acknowledgment | USINT     |        |         | •      |         |  |

|                | QuitCANIF1warning        | Bit 0     |        |         |        |         |  |

|                | QuitCANIF1passive        | Bit 1     |        |         |        |         |  |

|                | QuitCANIF1bussoff        | Bit 2     |        |         |        |         |  |

|                | QuitCANIF1RXoverrun      | Bit 3     |        |         |        |         |  |

|                | QuitCANIF2warning        | Bit 4     |        |         |        |         |  |

|                | QuitCANIF2passive        | Bit 5     |        |         |        |         |  |

|                | QuitCANIF2bussoff        | Bit 6     |        |         |        |         |  |

|                | QuitCANIF2RXoverrun      | Bit 7     |        |         |        |         |  |

#### 9.4 Function model 254 - Flatstream

Flatstream provides independent communication between an X2X Link master and the module. This interface was implemented as a separate function model for the CAN module. CAN information (identifier, status, etc.) is transferred via cyclic input and output registers. The sequence and control bytes are used to control this data stream (see "Flatstream communication" on page 17).

When using function model Flatstream, the user can choose whether to use library "AsFItGen" in AS for implementation or to adapt Flatstream handling directly to the individual requirements of the application.

## Information:

- Libraries "ArCAN" and "CAN\_Lib" cannot be used.

- Higher data rates can be achieved between X2X master and module compared to the "Flat" function model.

| SINT    | Cyclic                                  | Acyclic                                 | Cyclic |         |

|---------|-----------------------------------------|-----------------------------------------|--------|---------|

|         |                                         |                                         | Cyclic | Acyclic |

|         |                                         |                                         |        |         |

|         |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| IINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| IINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

|         |                                         |                                         |        |         |

| SINT    | •                                       |                                         |        |         |

| Bit 0   |                                         |                                         |        | İ       |

| Bit 1   |                                         |                                         |        | İ       |

| Bit 2   |                                         |                                         |        | İ       |

| Bit 3   |                                         |                                         |        | İ       |

| Bit 4   |                                         |                                         |        | İ       |

| Bit 5   |                                         |                                         |        | İ       |

| Bit 6   |                                         |                                         |        | İ       |

| Bit 7   |                                         |                                         |        | İ       |

| SINT    |                                         |                                         | •      |         |

| Bit 0   |                                         |                                         |        | İ       |

| Bit 1   |                                         |                                         |        | İ       |

| Bit 2   |                                         |                                         |        | İ       |

| Bit 3   |                                         |                                         |        | İ       |

| Bit 4   |                                         |                                         |        | İ       |

| Bit 5   |                                         |                                         |        | İ       |

| Bit 6   |                                         |                                         |        | İ       |

| Bit 7   |                                         |                                         |        | İ       |

| ,i.e. 1 |                                         |                                         |        |         |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| IINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

| SINT    |                                         |                                         |        | •       |

|         |                                         |                                         |        | •       |

| -       |                                         |                                         |        | •       |

|         |                                         |                                         |        | •       |

| 4 1     |                                         |                                         |        |         |

| SINT    |                                         |                                         |        |         |

|         |                                         |                                         |        |         |

|         |                                         |                                         |        |         |

|         |                                         |                                         |        |         |

|         | •                                       |                                         |        |         |

|         |                                         |                                         |        |         |

|         |                                         |                                         |        |         |

|         |                                         |                                         |        |         |

|         | BINT BINT BINT BINT BINT BINT BINT BINT | SINT SINT SINT SINT SINT SINT SINT SINT | SINT   | SINT    |

### 9.5 Function model 254 - Bus controller

The "Bus controller" function model is a reduced form of the "FlatStream" function model. Instead of up to 27 Tx / Rx bytes, a maximum of 7 Tx / Rx bytes can be used.

| Register        | Offset1)      | Name                                 | Data type | R      | lead       | V      | Vrite      |

|-----------------|---------------|--------------------------------------|-----------|--------|------------|--------|------------|

|                 |               |                                      |           | Cyclic | Non-cyclic | Cyclic | Non-cyclic |

| Interface - Con | figuration    |                                      |           |        |            |        |            |

| 257             | -             | Config01Baudrate                     | USINT     |        |            |        | •          |

| 259             | -             | Config01SJW                          | USINT     |        |            |        | •          |

| 261             | -             | Config01SPO                          | USINT     |        |            |        | •          |

| 266             | -             | Config01TXtrigger                    | UINT      |        |            |        | •          |

| 769             | -             | Config02Baudrate                     | USINT     |        |            |        | •          |

| 771             | -             | Config02SJW                          | USINT     |        |            |        | •          |

| 773             | -             | Config02SPO                          | USINT     |        |            |        | •          |

| 778             | -             | Config02TXtrigger                    | UINT      |        |            |        | •          |

| 6273            | -             | CfO_ErrorID0007                      | USINT     |        |            |        | •          |

| nterface - Com  | munication    |                                      |           |        |            |        |            |

| 6145            | -             | CAN error status                     | USINT     |        | •          |        |            |

|                 |               | CANIF1warning                        | Bit 0     |        |            |        |            |

|                 |               | CANIF1passive                        | Bit 1     |        |            |        |            |

|                 |               | CANIF1busoff                         | Bit 2     |        |            |        |            |

|                 |               | CANIF1RXoverrun                      | Bit 3     |        |            |        |            |

|                 |               | CANIF2warning                        | Bit 4     |        |            |        |            |

|                 |               | CANIF2passive                        | Bit 5     |        |            |        |            |

|                 |               | CANIF2busoff                         | Bit 6     |        |            |        |            |

|                 |               | CANIF2RXoverrun                      | Bit 7     |        |            |        |            |

| 6209            | _             | CAN error acknowledgment             | USINT     |        |            |        |            |

| 0209            | -             | QuitCANIF1warning                    | Bit 0     |        |            |        |            |

|                 |               | QuitCANIF1passive                    | Bit 1     |        |            |        |            |

|                 |               | QuitCANIF1passive QuitCANIF1bussoff  | Bit 2     |        |            |        |            |

|                 |               | QuitCANIF1busson QuitCANIF1RXoverrun | Bit 3     |        |            |        |            |

|                 |               |                                      |           |        |            |        |            |

|                 |               | QuitCANIF2 and in a                  | Bit 4     |        |            |        |            |

|                 |               | QuitCANIF2passive                    |           |        |            |        |            |

|                 |               | QuitCANIF2bussoff                    | Bit 6     |        |            |        |            |

| -1-101          |               | QuitCANIF2RXoverrun                  | Bit 7     |        |            |        |            |

| FlatStream - Co | ontiguration  | 10414771                             |           |        |            |        |            |

| 193             | -             | output01MTU                          | USINT     |        |            |        | •          |

| 195             | -             | input01MTU                           | USINT     |        |            |        | •          |

| 197             | -             | mode01                               | USINT     |        |            |        | •          |

| 199             | -             | forward01                            | USINT     |        |            |        | •          |

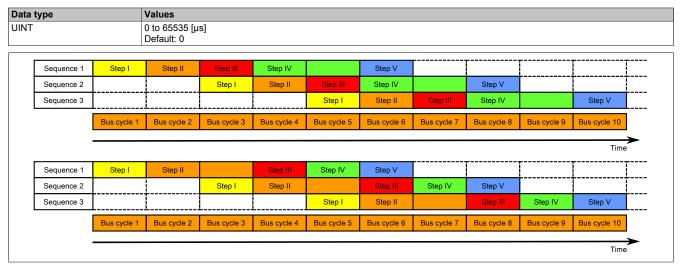

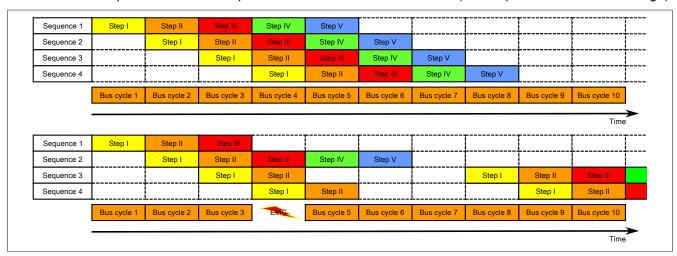

| 206             | -             | forwardDelay01                       | UINT      |        |            |        | •          |

| 209             | -             | output02MTU                          | USINT     |        |            |        | •          |

| 211             | -             | input02MTU                           | USINT     |        |            |        | •          |

| 213             | -             | mode02                               | USINT     |        |            |        | •          |

| 215             | -             | forward02                            | USINT     |        |            |        | •          |

| 222             | -             | forwardDelay02                       | UINT      |        |            |        | •          |

| FlatStream - Co | mmunication   |                                      |           |        |            |        |            |

| 0               | 0             | Input01Sequence                      | USINT     | •      |            |        |            |

| 64              | 8             | Input02Sequence                      | USINT     | •      |            |        |            |

| Index * 1 + 0   | Index * 1 + 0 | Rx01Byte1 to Rx01Byte7               | USINT     | •      |            |        |            |

| Index * 1 + 64  | Index * 1 + 8 |                                      | USINT     | •      |            |        |            |

| 32              | 0             | Output01Sequence                     | USINT     |        |            | •      |            |

| 96              | 8             | Output02Sequence                     | USINT     |        |            | •      |            |

| Index * 1 + 32  | Index * 1 + 0 | Tx01Byte1 to Tx01Byte7               | USINT     |        |            | •      |            |

| Index * 1 + 96  | Index * 1 + 8 | Tx02Byte1 to Tx02Byte7               | USINT     |        |            | •      |            |

<sup>1)</sup> The offset specifies the position of the register within the CAN object.

### 9.5.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X20 user's manual (version 3.50 or later).

## 9.5.2 CAN I/O bus controller

The module occupies 2 analog logical slots on CAN I/O.

## 9.6 Using this module with SGC target systems

## Information:

This module can only be used with SGC target systems if the function model is set to "Flatstream" or "Flat".

### 9.7 CAN object

A CAN object is always made up of a 4-byte identifier and a maximum of 8 subsequent data bytes. This also results in the relationship between CAN object length and the amount of CAN payload data. This is important because the number of CAN payload data bytes for communication via "FlatStream" always has to be determined using the frame length.

#### Composition of a CAN object / CAN frame

| Bytes  | Function         | Information                   |

|--------|------------------|-------------------------------|

| 1      | Code             | ID bit 0 to 7                 |

| 2      |                  | ID bit 8 to 15                |

| 3      |                  | ID bit 16 to 23               |

| 4      |                  | ID bit 24 to 31               |

| 5 - 12 | CAN payload data | 0 to 8 CAN payload data bytes |

#### Code

The 32 bits (4 bytes) of the CAN identifier are used as follows:

| Bit    | Description                                   | Value | Information                                            |

|--------|-----------------------------------------------|-------|--------------------------------------------------------|

| 0      | Frame format                                  | 0     | Standard frame format (SFF) with an 11-bit identifier  |

|        |                                               | 1     | Extended frame format (EFF) with an 29-bit identifier  |

| 1      | Frame type                                    | 0     | Data frame                                             |

|        |                                               | 1     | Remote frame (RTR)                                     |

| 2      | Reserved                                      | -     |                                                        |

| 3 - 31 | CAN identifier for telegram to be transmitted | х     | Extended frame format (EFF) with 29 bits               |

|        |                                               |       | Standard frame format (SFF) with 11 bits <sup>1)</sup> |

<sup>1)</sup> Only bits 21 to 31 are used; bits 3 to 20 = 0.

### 9.7.1 CAN module data stream

In function model 254, the data packets to be transferred in a data stream are referred to as frames.

### Information:

For the CAN module, that means:

- A frame always contains one CAN object and therefore cannot be longer than 12 bytes.

- The CAN object is only transferred to the transmit buffer after the frame has been completed.

- The CAN payload data length has a fixed relationship with the frame length and the actual size

of the CAN object. The following rules apply:

- CAN payload data length = Frame length 4

- Frame length = CAN payload data length + 4

## 9.8 Interface - Configuration

#### 9.8.1 Transfer rate

Name:

Config01Baudrate to Config02Baudrate

"Baud rate" in the Automation Studio I/O configuration.

Configuration of the CAN transfer rate for the respective interface.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit   | Description   | Value | Information                                         |

|-------|---------------|-------|-----------------------------------------------------|

| 0 - 3 | Transfer rate | 0     | Interface disabled (bus controller default setting) |

|       |               | 1     | 10 kbit/s                                           |

|       |               | 2     | 20 kbit/s                                           |

|       |               | 3     | 50 kbit/s                                           |

|       |               | 4     | 100 kbit/s                                          |

|       |               | 5     | 125 kbit/s                                          |

|       |               | 6     | 250 kbit/s                                          |

|       |               | 7     | 500 kbit/s                                          |

|       |               | 8     | 800 kbit/s                                          |

|       |               | 9     | 1000 kbit/s                                         |

| 4 - 7 | Reserved      | -     |                                                     |

### 9.8.2 Synchronization Jump Width

Name

Config01SJW to Config02SJW

"Synchronization jump width" in the Automation Studio I/O configuration.

The synchronization jump width (SJW) is used to resynchronize the sample point within a CAN telegram.

A detailed description of the SJW can be found in the CAN specification.

| Data type | Value  | Meaning                           |  |

|-----------|--------|-----------------------------------|--|

| USINT     | 0 to 4 | Synchronization jump width.       |  |

|           |        | Bus controller default setting: 3 |  |

### 9.8.3 Offset for the sampling instant

Name:

Config01SPO to Config02SPO

"Sample point offset" in the Automation Studio I/O configuration.

Offset for the sample point of the individual bits on the CAN bus.

A detailed description of the SPO can be found in the CAN specification.

| Data type | Value  | Meaning                           |  |

|-----------|--------|-----------------------------------|--|

| USINT     | 0 to 1 | Sample point offset.              |  |

|           |        | Bus controller default setting: 0 |  |

#### 9.8.4 Start of transmission

Name:

Config01TXtrigger to Config02TXtrigger

"TX objects / TX triggers" in the Automation Studio I/O configuration.

Defines the number of CAN objects that must be copied to the transmit buffer before the transmission is started.

| Data type | Value  | Meaning                                                                      |  |

|-----------|--------|------------------------------------------------------------------------------|--|

| UINT      | 0 to 8 | Number of CAN objects in the transmit buffer before transmission is started. |  |

|           |        | Bus controller default setting: 1                                            |  |

### 9.8.5 Configuration of error messages

Name:

CfO ErrorID0007

This register must be used first to configure the error messages that have to be transferred. If the corresponding enable bit is not set, no error status will be sent to the higher-level system when the error occurs.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

#### Bit structure:

| Bit | Description     | Value | Information                               |

|-----|-----------------|-------|-------------------------------------------|

| 0   | CANIF1warning   | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

| 1   | CANIF1passive   | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

| 2   | CANIF1bussoff   | 0     | Disabled (bus controller default setting) |

| İ   |                 | 1     | Enabled                                   |

| 3   | CANIF1RXoverrun | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

| 4   | CANIF2warning   | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

| 5   | CANIF2passive   | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

| 6   | CANIF2bussoff   | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

| 7   | CANIF2RXoverrun | 0     | Disabled (bus controller default setting) |

|     |                 | 1     | Enabled                                   |

#### 9.8.6 Size of the transmit buffer

Name:

Cfo\_FIFOTXlimit01 to Cfo\_FIFOTXlimit02

"TX FIFO size" in the Automation Studio I/O configuration.

Determines the size of the transmit buffer for the respective interface.

| Data type | Value   | Meaning                     |

|-----------|---------|-----------------------------|

| USINT     | 0 to 18 | Size of the transmit buffer |

## 9.8.7 Display of unprocessed elements remaining in transmit/receive buffer

Name:

Cfo\_TXRXinfoFlags01 to Cfo\_TXRXinfoFlags02

This register can be used to specify that the number of unprocessed elements in the transmit and receive buffers is indicated in the upper 4 bits of the "TX0[x]CountReadBack" and "RX0[x]Count" registers for the respective interface.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit   | Description                                                           | Value | Information                                                                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | TxFifoInfo "Mode of channel TX0[x]CountReadBack" in the Automation    | 0     | The "TX0[x]Count" is read in the "TX0[x]CountReadBack" on page 13 register.                                                                                                                                                 |

|       | Studio I/O configuration                                              | 1     | The "TX0[x]Count" is read in the "TX0[x]CountReadBack" on page 13 register.  The upper 4 bits are used to return the number of frames in the transmit buffer that have not been transmitted.                                |

| 1     | RxFifoInfo "Mode of channel RX0[x]Count" in the Automation Studio I/O | 0     | The number of received telegrams is shown in the "RX0[x]Count" on page 14 register.                                                                                                                                         |

|       | configuration                                                         | 1     | The number of received telegrams is shown in the lower 4 bits of the "RX0[x]Count" on page 14 register.  The upper 4 bits are used to indicate the number of received but not acknowledged telegrams in the receive buffer. |

| 2 - 7 | Reserved                                                              | -     |                                                                                                                                                                                                                             |

#### 9.9 Interface - Communication

#### 9.9.1 CAN error status

Name:

CAN error status

The bits in this register indicate the error states defined in the CAN protocol. If an error occurs, the corresponding bit is set. For an error bit to be reset, the corresponding bit must be acknowledged (see "CAN error acknowledgment" on page 13).

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit | Description     | Value | Information                        |

|-----|-----------------|-------|------------------------------------|

| 0   | CANIF1warning   | 0     | No error                           |

|     |                 | 1     | CANwarning Error occurred on IF1   |

| 1   | CANIF1passive   | 0     | No error                           |

|     |                 | 1     | CANpassive Error occurred on IF1   |

| 2   | CANIF1busoff    | 0     | No error                           |

|     |                 | 1     | CANbusoff Error occurred on IF1    |

| 3   | CANIF1RXoverrun | 0     | No error                           |

|     |                 | 1     | CANRXoverrun Error occurred on IF1 |

| 4   | CANIF2warning   | 0     | No error                           |

|     |                 | 1     | CANwarning Error occurred on IF2   |

| 5   | CANIF2passive   | 0     | No error                           |

|     |                 | 1     | CANpassive Error occurred on IF2   |

| 6   | CANIF2busoff    | 0     | No error                           |

|     |                 | 1     | CANbusoff Error occurred on IF2    |

| 7   | CANIF2RXoverrun | 0     | No error                           |

|     |                 | 1     | CANRXoverrun Error occurred on IF2 |

### **CANwarning**

A faulty frame was detected on the CAN bus. This can include bit errors, bit stuffing errors, CRC errors, format errors in the telegram and acknowledgment errors, for example.

### **CANpassive**

The internal transmit and/or receive error counter is greater than 127. CAN communication continues to run, but the interface can only issue a "passive error frame". Likewise, "error passive stations" have less ability to send new telegrams altogether.

### **CANbusoff**

The internal transmit error counter is greater than 255. The bus is switched off, and CAN communication with the module no longer takes place.

#### **CANRXoverrun**

An overflow occurred in the module's receive buffer.

## 9.9.2 CAN error acknowledgment

Name:

CAN error acknowledgment

Setting the bits in this register acknowledges the error assigned to the bit and clears the corresponding bit in the "CAN error status" register. The application thus informs the module that it has recognized the error state.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit | Description         | Value | Information                           |

|-----|---------------------|-------|---------------------------------------|

| 0   | QuitCANIF1warning   | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANwarning error on IF1   |

| 1   | QuitCANIF1passive   | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANpassive error on IF1   |

| 2   | QuitCANIF1bussoff   | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANbusoff error on IF1    |

| 3   | QuitCANIF1RXoverrun | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANRXoverrun error on IF1 |

| 4   | QuitCANIF2warning   | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANwarning error on IF2   |

| 5   | QuitCANIF2passive   | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANpassive error on IF2   |

| 6   | QuitCANIF2bussoff   | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANbusoff error on IF2    |

| 7   | QuitCANIF2RXoverrun | 0     | No acknowledgment                     |

|     |                     | 1     | Acknowledge CANRXoverrun error on IF2 |

### 9.9.3 New CAN telegram for transmit buffer

Name:

TX01Count to TX02Count

By increasing this value, the application notifies the module that a new CAN telegram should be transferred into the transmit buffer.

| Data type | Value    |

|-----------|----------|

| USINT     | 0 to 255 |

# 9.9.4 Read "TX0[x]Count"

Name:

TX01CountReadBack to TX02CountReadBack

The value of "TX0[x]Count" is copied from the module into this register. This makes it possible for the application task to verify that the CAN telegram data was transfered from the module correctly.

The meaning of the value depends on the "TxFifoInfo" bit. This is located in the register "Cfo\_TXRXinfoFlags0[x]" on page 11.

| Data type | Value    | "TxFifoInfo" bit | Meaning            |

|-----------|----------|------------------|--------------------|

| USINT     | 0 to 255 | 0                | Read "TX0[x]Count" |

|           |          | 1                | See bit structure. |

## Bit structure:

|   | Bit   | Function                                                               | Value   | Information                                                                         |

|---|-------|------------------------------------------------------------------------|---------|-------------------------------------------------------------------------------------|

| ſ | 0 - 3 | Read "TX0[x]Count"                                                     | 0 to 15 | Only the lower 4 bits                                                               |

|   | 4 - 7 | Number of frames in the transmit buffer that have not been transmitted | 0 to 15 | If this number exceeds the 15 (a maximum of 18 possible), the value 15 is returned. |

## 9.9.5 Counter for received CAN telegrams

Name:

RX01Count to RX02Count

This counter is increased by 1 with each CAN telegram. The application task can thus detect when new data is received and get it from the corresponding "RX0[x]Data" registers.

The meaning of the value depends on the "Cfo\_TXRXinfoFlags0[x]" on page 11 bit in the "Cfo\_TXRXinfoFlags" register.

| Data type | Value    | "RxFifoInfo" bit | Meaning                        |  |

|-----------|----------|------------------|--------------------------------|--|

| USINT     | 0 to 255 | 0                | Counter for received telegrams |  |

|           |          | 1                | See bit structure.             |  |

### Bit structure:

| Bit   | Function                                                 | Value   | Information           |

|-------|----------------------------------------------------------|---------|-----------------------|

| 0 - 3 | Counter for received telegrams                           | 0 to 15 | Only the lower 4 bits |

| 4 - 7 | Number of unacknowledged telegrams in the receive buffer | 0 to 15 |                       |

#### 9.10 Transmit buffer for IF1 and IF2

### 9.10.1 Number of CAN payload data bytes

Name:

TX01DataSize to TX02DataSize

Number of CAN payload data bytes to be transmitted If a value less than 0 is specified here, this CAN telegram is marked as being invalid and is not transferred into the transmit buffer. This is useful in connection with transmit error detection between the module and the CPU (see "Taking possible errors into consideration when transmitting" on page 15).

| Data type | Value     | Meaning                                      |

|-----------|-----------|----------------------------------------------|

| USINT     | -128 to 8 | Amount of CAN payload data to be transmitted |

#### 9.10.2 Identifier of the CAN telegram to be transmitted.

Name:

TX01Ident to TX02Ident

Identifier of the CAN telegram to be transmitted. The frame format and the identifier format are also defined in this register.

| Data type | Values                 |

|-----------|------------------------|

| UDINT     | See the bit structure. |

#### Bit structure:

| Bit    | Description                                   | Value | Information                                                                                        |

|--------|-----------------------------------------------|-------|----------------------------------------------------------------------------------------------------|

| 0      | Frame format                                  | 0     | Standard frame format (SFF) with an 11-bit identifier                                              |

|        |                                               | 1     | Extended frame format (EFF) with an 29-bit identifier                                              |

| 1      | Frame type                                    | 0     | Data frame                                                                                         |

|        |                                               | 1     | Remote frame (RTR)                                                                                 |

| 2      | Reserved                                      | -     |                                                                                                    |

| 3 - 31 | CAN identifier for telegram to be transmitted | х     | Extended frame format (EFF) with 29 bits<br>Standard frame format (SFF) with 11 bits <sup>1)</sup> |

<sup>1)</sup> Only bits 21 to 31 are used; bits 3 to 20 = 0.

### 9.10.3 Configuration of the CAN payload data being sent

Name:

TX0[x]DataByte0 to TX0[x]DataByte7

TX0[x]DataWord0 to TX0[x]DataWord3

TX0[x]DataLong0 to TX0[x]DataLong1

CAN payload data in the transmit direction. The 8 payload data bytes for a telegram can be used as data points with 8 individual bytes, 4 words or 2 longs as needed.

| Data type | Value              | Description                           |  |

|-----------|--------------------|---------------------------------------|--|

| USINT     | 0 to 255           | CAN payload data transmitted as bytes |  |

| UINT      | 0 to 65,535        | CAN payload data transmitted as words |  |

| UDINT     | 0 to 4.294.967.295 | CAN payload data transmitted as longs |  |

## 9.10.4 Taking possible errors into consideration when transmitting

Data on the POWERLINK network or X2X Link can be lost due to transmission errors. One-time failures of cyclic data are tolerated by the I/O systems. This is possible since all I/O data is re-transferred in the subsequent cycle. A transfer error cannot be detected from the I/O variables; they remain frozen on the value from the last cycle.

These tolerated one-time I/O failures can lead to data loss or the delayed CAN telegram transmission. The counter feedback is derived on the module and used to detect these cases.

Register for counter feedback: "TX0[x]CountReadBack" on page 13

#### 9.11 Receive buffer for IF1 and IF2

## 9.11.1 Number of valid CAN payload data bytes

Name:

RX01DataSize to RX02DataSize

Number of valid CAN payload data bytes.

This register also uses the value -1 (0xFF) to indicate a general error or gap in the input data stream. Details regarding the error that has occurred can be seen in the "CAN error status" on page 12 register.

| Data type | Value  | Meaning                 |  |

|-----------|--------|-------------------------|--|

| USINT     | 1 to 8 | Number CAN payload data |  |

| -1 E      |        | Error                   |  |

#### 9.11.2 Identifier of the received data

Name:

RX01Ident to RX02Ident

Identifiers assigned to the received data. The frame format and the identifier format can also be read from this register.

| Data type | Values                 |

|-----------|------------------------|

| UDINT     | See the bit structure. |

#### Bit structure:

| Bit    | Description                                   | Value | Information                                            |

|--------|-----------------------------------------------|-------|--------------------------------------------------------|

| 0      | Frame format                                  | 0     | Standard frame format (SFF) with an 11-bit identifier  |

|        |                                               | 1     | Extended frame format (EFF) with an 29-bit identifier  |

| 1      | Frame type                                    | 0     | Data frame                                             |

|        |                                               | 1     | Remote frame (RTR)                                     |

| 2      | Reserved                                      | -     |                                                        |

| 3 - 31 | CAN identifier for telegram to be transmitted | х     | Extended frame format (EFF) with 29 bits               |

|        |                                               |       | Standard frame format (SFF) with 11 bits <sup>1)</sup> |

<sup>1)</sup> Only bits 21 to 31 are used; bits 3 to 20 = 0.

### 9.11.3 Configuration of the CAN payload data to be received

Name:

RX0[x]DataByte0 to RX0[x]DataByte7

RX0[x]DataWord0 to RX0[x]DataWord3

RX0[x]DataLong0 to RX0[x]DataLong1

These registers hold the payload data of the CAN object to be transferred from the receive buffer to the CPU in the current cycle. If new data is received or if the receive buffer contains additional CAN objects, these registers are overwritten with the new data in the next cycle.

To avoid losing CAN objects, the application must respond immediately to a change in the "RX0[x]Count" and copies the data from these registers.

The maximum 8 bytes for a CAN telegram can be used as data points with 8 individual bytes, 4 words or 2 longs as needed.

| Data type | Value              | Description                        |  |  |  |

|-----------|--------------------|------------------------------------|--|--|--|

| USINT     | 0 to 255           | Received CAN payload data as bytes |  |  |  |

| UINT      | 0 to 65,535        | Received CAN payload data as words |  |  |  |

| UDINT     | 0 to 4.294.967.295 | Received CAN payload data as longs |  |  |  |

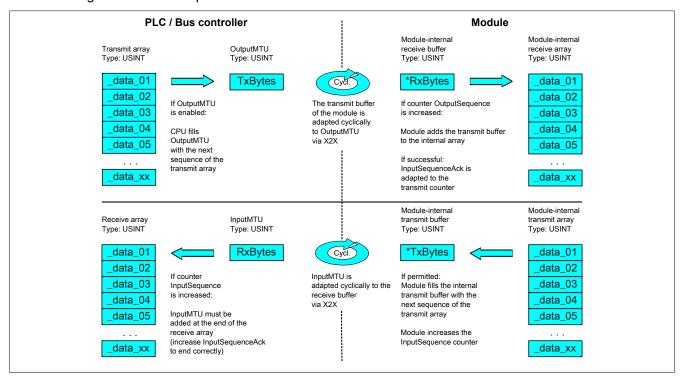

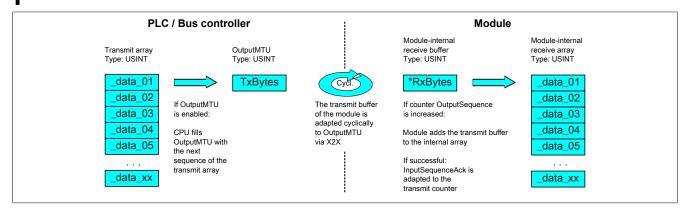

#### 9.12 Flatstream communication

#### 9.12.1 Introduction

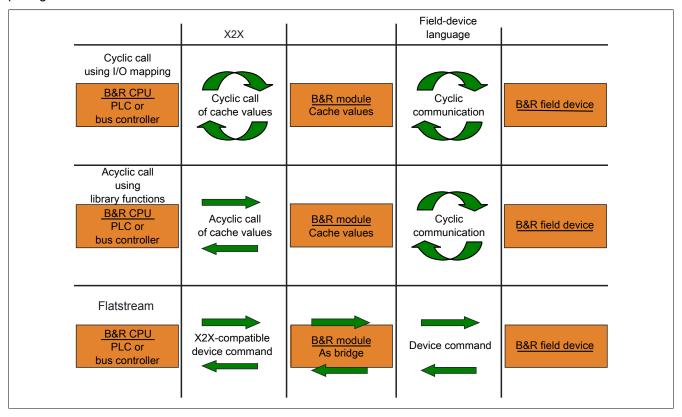

B&R offers an additional communication method for some modules. "Flatstream" was designed for X2X and POWERLINK networks and allows data transmission to be adapted to individual demands. Although this method is not 100% real-time capable, it still allows data transfer to be handled more efficiently than with standard cyclic polling.

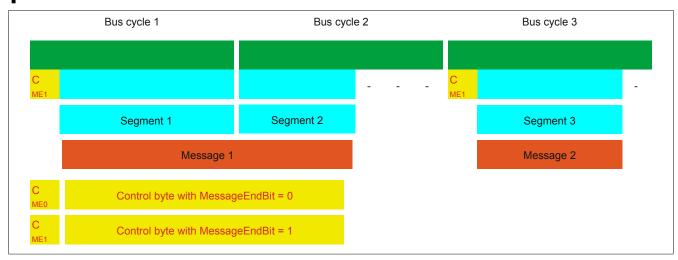

Figure 1: 3 types of communication

Flatstream extends cyclic and acyclic data queries. With Flatstream communication, the module acts as a bridge. The module is used to pass CPU queries directly on to the field device.

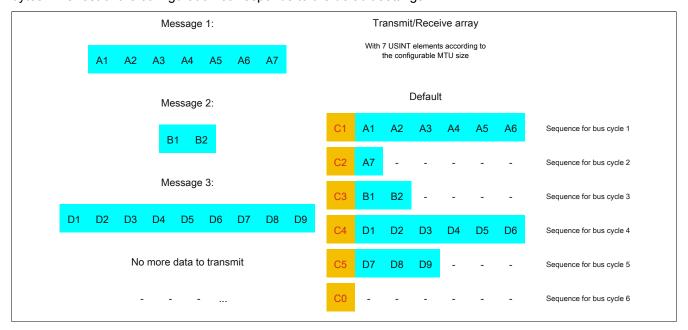

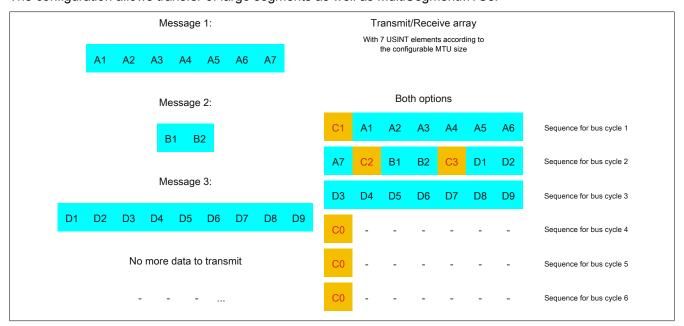

#### 9.12.2 Message, segment, sequence, MTU

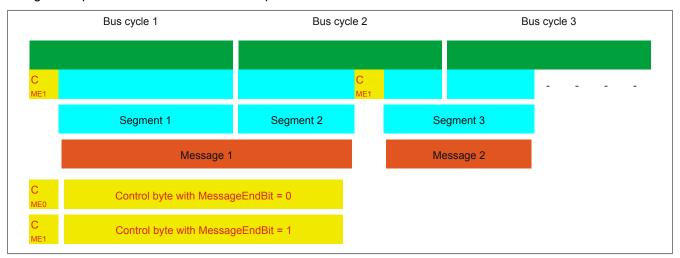

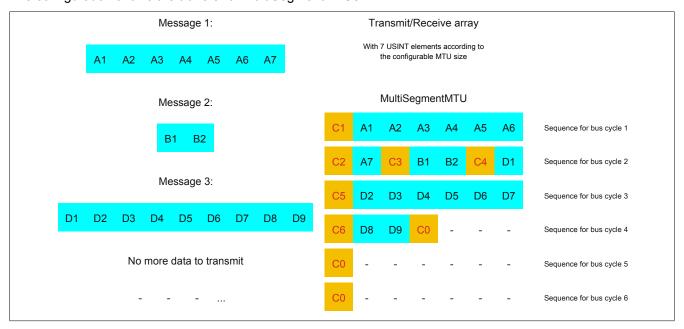

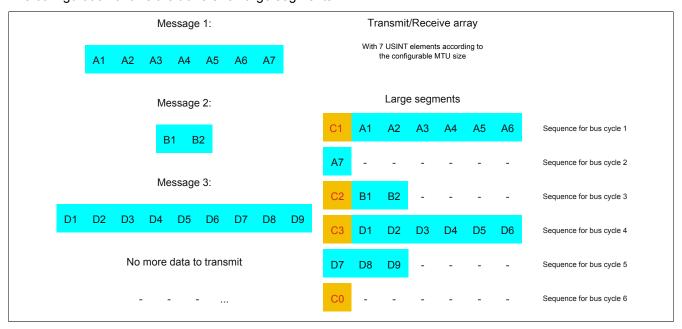

The physical properties of the bus system limit the amount of data that can be transmitted during one bus cycle. With Flatstream communication, all messages are viewed as part of a continuous data stream. Long data streams must be broken down into several fragments that are sent one after the other. To understand how the receiver puts these fragments back together to get the original information, it is important to understand the difference between a message, a segment, a sequence and an MTU.

#### Message

A message refers to information exchanged between 2 communicating partner stations. The length of a message is not restricted by the Flatstream communication method. Nevertheless, module-specific limitations must be considered.

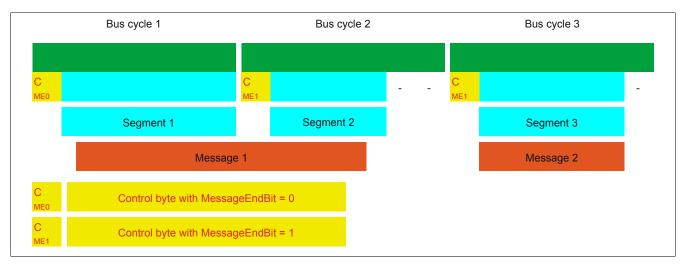

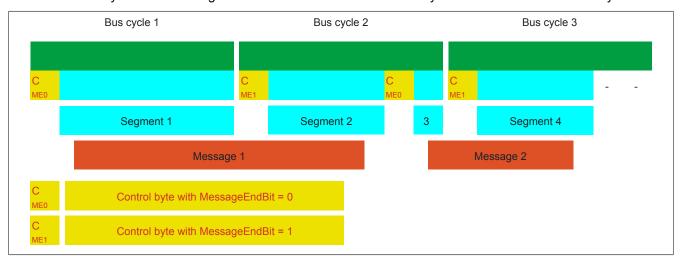

### Segment (logical division of a message):

A segment has a finite size and can be understood as a section of a message. The number of segments per message is arbitrary. So that the recipient can correctly reassemble the transferred segments, each segment is preceded by a byte with additional information. This control byte contains information such as the length of a segment and whether the approaching segment completes the message. This makes it possible for the receiving station to interpret the incoming data stream correctly.

### Sequence (how a segment must be arranged physically):

The maximum size of a sequence corresponds to the number of enabled Rx or Tx bytes (later: "MTU"). The transmitting station splits the transmit array into valid sequences. These sequences are then written successively to the MTU and transferred to the receiving station where they are put back together again. The receiver stores the incoming sequences in a receive array, obtaining an image of the data stream in the process.

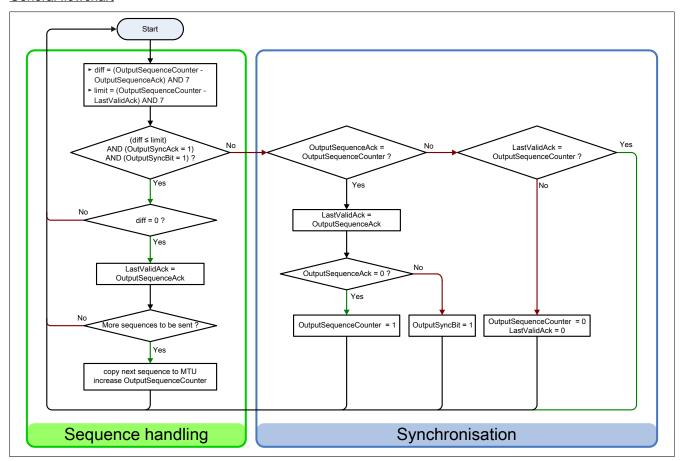

With Flatstream communication, the number of sequences sent are counted. Successfully transferred sequences must be acknowledged by the receiving station to ensure the integrity of the transfer.

### MTU (Maximum Transmission Unit) - Physical transport:

MTU refers to the enabled USINT registers used with Flatstream. These registers can accept at least one sequence and transfer it to the receiving station. A separate MTU is defined for each direction of communication. OutputMTU defines the number of Flatstream Tx bytes, and InputMTU specifies the number of Flatstream Rx bytes. The MTUs are transported cyclically via the X2X Link network, increasing the load with each additional enabled USINT register.

#### **Properties**

Flatstream messages are not transferred cyclically or in 100% real time. Many bus cycles may be needed to transfer a particular message. Although the Rx and Tx registers are exchanged between the transmitter and the receiver cyclically, they are only processed further if explicitly accepted by register "InputSequence" or "OutputSequence".

#### Behavior in the event of an error (brief summary)

The protocol for X2X and POWERLINK networks specifies that the last valid values should be retained when disturbances occur. With conventional communication (cyclic/acyclic data queries), this type of error can generally be ignored.

In order for communication to also take place without errors using Flatstream, all of the sequences issued by the receiver must be acknowledged. If Forward functionality is not used, then subsequent communication is delayed for the length of the disturbance.

If Forward functionality is being used, the receiving station receives a transmission counter that is incremented twice. The receiver stops, i.e. it no longer returns any acknowledgments. The transmitting station uses SequenceAck to determine that the transmission was faulty and that all affected sequences must be repeated.

#### 9.12.3 The Flatstream principle

#### Requirement

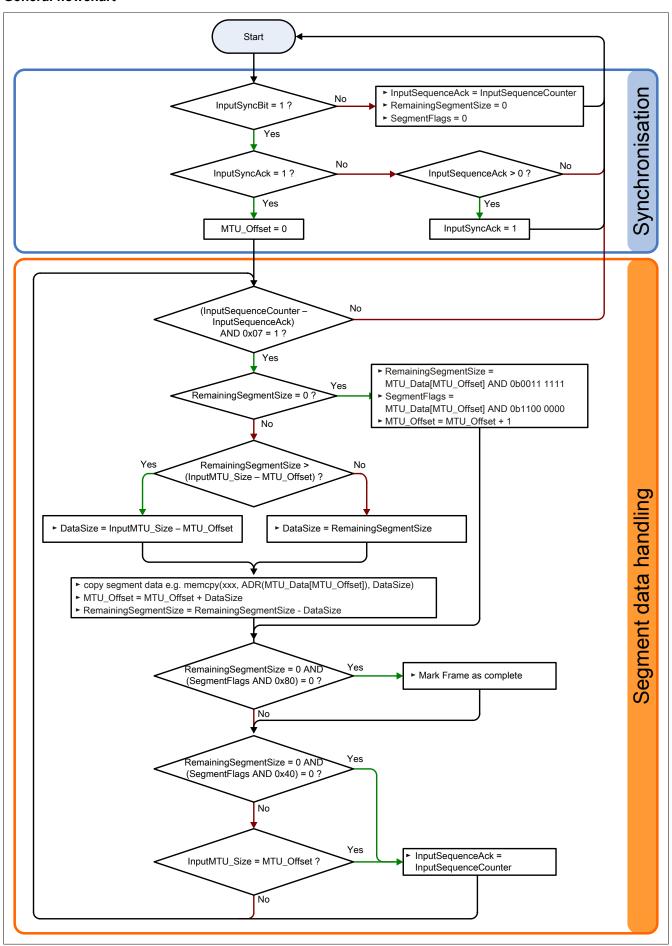

Before Flatstream can be used, the respective communication direction must be synchronized, i.e. both communication partners cyclically query the sequence counter on the opposite station. This checks to see if there is new data that should be accepted.

#### Communication

If a communication partner wants to transmit a message to its opposite station, it should first create a transmit array that corresponds to Flatstream conventions. This allows the Flatstream data to be organized very efficiently without having to block other important resources.

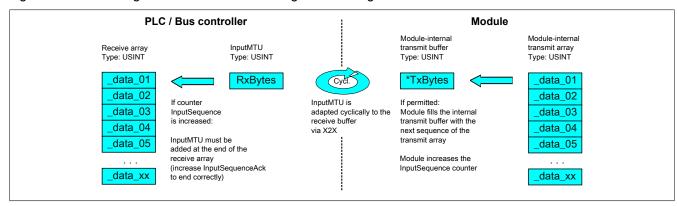

Figure 2: Flatstream communication

### Procedure

The first thing that happens is that the message is broken into valid segments of up to 63 bytes, and the corresponding control bytes are created. The data is formed into a data stream made up of one control bytes per associated segment. This data stream can be written to the transmit array. The maximum size of each array element matches that of the enabled MTU so that one element corresponds to one sequence.

If the array has been completely created, the transmitter checks whether the MTU is permitted to be refilled. It then copies the first element of the array or the first sequence to the Tx byte registers. The MTU is transported to the receiver station via X2X Link and stored in the corresponding Rx byte registers. To signal that the data should be accepted by the receiver, the transmitter increases its SequenceCounter.

If the communication direction is synchronized, the opposite station detects the incremented SequenceCounter. The current sequence is appended to the receive array and acknowledged by SequenceAck. This acknowledgment signals to the transmitter that the MTU can now be refilled.

If the transfer is successful, the data in the receive array will correspond 100% to the data in the transmit array. During the transfer, the receiving station must detect and evaluate the incoming control bytes. A separate receive array should be created for each message. This allows the receiver to immediately begin further processing of messages that are completely transferred.

#### 9.12.4 Registers for Flatstream mode

5 registers are available for configuring Flatstream. The default configuration can be used to transmit small amounts of data relatively easily.

## Information:

The CPU communicates directly with the field device via registers "OutputSequence" and "InputSequence" as well as the enabled Tx and Rx bytes. For this reason, the user needs to have sufficient knowledge of the communication protocol being used on the field device.

#### 9.12.4.1 Flatstream configuration

To use Flatstream, the program sequence must first be expanded. The cycle time of the Flatstream routines must be set to a multiple of the bus cycle. Other program routines should be implemented in Cyclic #1 to ensure data consistency.

At the absolute minimum, registers "InputMTU" and "OutputMTU" must be set. All other registers are filled in with default values at the beginning and can be used immediately. These registers are used for additional options, e.g. to transfer data in a more compact way or to increase the efficiency of the general procedure.

The Forward registers extend the functionality of the Flatstream protocol. This functionality is useful for substantially increasing the Flatstream data rate, but it also requires quite a bit of extra work when creating the program sequence.

#### 9.12.4.1.1 Number of enabled Tx and Rx bytes

Name: OutputMTU InputMTU

These registers define the number of enabled Tx or Rx bytes and thus also the maximum size of a sequence. The user must consider that the more bytes made available also means a higher load on the bus system.

### Information:

In the rest of this description, the names "OutputMTU" and "InputMTU" do not refer to the registers explained here. Instead, they are used as synonyms for the currently enabled Tx or Rx bytes.

| Data type | Values                                                              |

|-----------|---------------------------------------------------------------------|

| USINT     | See the module-specific register overview (theoretically: 3 to 27). |

#### 9.12.4.2 Flatstream operation

When using Flatstream, the communication direction is very important. For transmitting data to a module (output direction), Tx bytes are used. For receiving data from a module (input direction), Rx bytes are used.