# X20MM4456

# **1** General information

The PWM motor bridge module is used to control 4 DC motors with a nominal voltage of 24 to 48 VDC  $\pm$ 25% at a nominal current up to 6 A. The module can be reconfigured and used in current controller mode for controlling inductive loads. The module is also equipped with 16 digital inputs, which can be used as incremental counters. The 4 motors are controlled with a full-bridge (H-bridge). This enables the motors to be moved in both directions.

- 4x outputs (H bridge) with PWM control and 24 to 48 VDC ±25% supply

- 6 A nominal current (10 A max current)

- 15 Hz to 50 kHz frequency, 16-bit

- PWM resolution, 15-bit, + sign, minimum 10 ns

- Configurable dither

- 4x 4 inputs 24V, can be configured as ABR

- Sink connection

- 1-wire connections

# 2 Order data

Table 1: X20MM4456 - Order data

# 3 Technical data

| Order number                                                     | X20MM4456                                                |  |  |  |  |

|------------------------------------------------------------------|----------------------------------------------------------|--|--|--|--|

| Short description                                                |                                                          |  |  |  |  |

| I/O module                                                       | 4-channel PWM motor bridge, 4 ABR incremental encoders   |  |  |  |  |

| General information                                              |                                                          |  |  |  |  |

| B&R ID code                                                      | 0xA177                                                   |  |  |  |  |

| Status indicators                                                | I/O function per channel, operating state, module status |  |  |  |  |

| Diagnostics                                                      |                                                          |  |  |  |  |

| Module run/error                                                 | Yes, using LED status indicator and software             |  |  |  |  |

| Output                                                           | Yes, using LED status indicator and software             |  |  |  |  |

| •                                                                | -                                                        |  |  |  |  |

| I/O power supply                                                 | Yes, using software                                      |  |  |  |  |

| Power consumption                                                | 0.04 W                                                   |  |  |  |  |

| Bus<br>Internal I/O                                              | 0.01 W                                                   |  |  |  |  |

|                                                                  | 2.4 W                                                    |  |  |  |  |

| External I/O 50 kHz                                              | 0.0111/1.1                                               |  |  |  |  |

| 24 VDC                                                           | 3.3 W / channel                                          |  |  |  |  |

| 48 VDC                                                           | 4.7 W / channel                                          |  |  |  |  |

| 60 VDC                                                           | 5.4 W / channel                                          |  |  |  |  |

| External I/O 10 kHz                                              |                                                          |  |  |  |  |

| 24 VDC                                                           | 2.1 W / channel                                          |  |  |  |  |

| 48 VDC                                                           | 2.4 W / channel                                          |  |  |  |  |

| 60 VDC                                                           | 2.6 W / channel                                          |  |  |  |  |

| External I/O 5 kHz                                               |                                                          |  |  |  |  |

| 24 VDC                                                           | 2 W / channel                                            |  |  |  |  |

| 48 VDC                                                           | 2.1 W / channel                                          |  |  |  |  |

| 60 VDC                                                           | 2.2 W / channel                                          |  |  |  |  |

| Additional power dissipation caused by actuators (resistive) [W] | -                                                        |  |  |  |  |

| Certifications                                                   |                                                          |  |  |  |  |

| CE                                                               | Yes                                                      |  |  |  |  |

| ATEX                                                             | Zone 2, II 3G Ex nA nC IIA T5 Gc                         |  |  |  |  |

|                                                                  | IP20, Ta (see X20 user's manual)                         |  |  |  |  |

|                                                                  | FTZÚ 09 ATEX 0083X                                       |  |  |  |  |

| UL                                                               | cULus E225616                                            |  |  |  |  |

|                                                                  | Power conversion equipment                               |  |  |  |  |

| HazLoc                                                           | cCSAus 244665                                            |  |  |  |  |

|                                                                  | Process control equipment                                |  |  |  |  |

|                                                                  | for hazardous locations                                  |  |  |  |  |

| EAC                                                              | Class I, Division 2, Groups ABCD, T5<br>Yes              |  |  |  |  |

| KC                                                               | Yes                                                      |  |  |  |  |

|                                                                  | les                                                      |  |  |  |  |

| Digital inputs                                                   | 16                                                       |  |  |  |  |

| Quantity                                                         |                                                          |  |  |  |  |

| Nominal voltage                                                  | 24 VDC                                                   |  |  |  |  |

| Input characteristics per EN 61131-2                             |                                                          |  |  |  |  |

| Input voltage                                                    | 24 VDC (-15% / +20%)                                     |  |  |  |  |

| Input current at 24 VDC                                          | Approx. 4 mA                                             |  |  |  |  |

| Input circuit                                                    | Sink                                                     |  |  |  |  |

| Input filter                                                     |                                                          |  |  |  |  |

| Hardware                                                         | <5 µs                                                    |  |  |  |  |

| Software                                                         |                                                          |  |  |  |  |

| Connection type                                                  | 1-wire connections                                       |  |  |  |  |

| Input resistance                                                 | Typ. 6 kΩ                                                |  |  |  |  |

| Additional functions                                             | 4x ABR incremental encoder                               |  |  |  |  |

| Switching threshold                                              |                                                          |  |  |  |  |

| Low                                                              | <5 VDC                                                   |  |  |  |  |

| High                                                             | >15 VDC                                                  |  |  |  |  |

| Insulation voltage between channel and bus                       | 500 $V_{eff}$                                            |  |  |  |  |

| ABR incremental encoder                                          |                                                          |  |  |  |  |

| Quantity                                                         | 4                                                        |  |  |  |  |

| Encoder inputs                                                   | 24 V, asymmetrical                                       |  |  |  |  |

| Counter size                                                     | 16-bit                                                   |  |  |  |  |

| Input frequency                                                  | Max. 50 kHz                                              |  |  |  |  |

| Evaluation                                                       | 4x                                                       |  |  |  |  |

| Signal form                                                      | Square wave pulse                                        |  |  |  |  |

| PWM output                                                       |                                                          |  |  |  |  |

| Quantity                                                         | 4                                                        |  |  |  |  |

| Nominal voltage                                                  | 24 to 48 VDC ±25% <sup>1)</sup>                          |  |  |  |  |

| Nominal current                                                  | 6 A                                                      |  |  |  |  |

| Maximum current                                                  | 10 A (2 s)                                               |  |  |  |  |

|                                                                  | 10 A (2 S)<br>15 Hz to 50 kHz                            |  |  |  |  |

| PWM frequency                                                    |                                                          |  |  |  |  |

Table 2: X20MM4456 - Technical data

| Order number                               | X20MM4456                                                                                       |  |  |  |  |

|--------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|--|

| Actuator power supply                      |                                                                                                 |  |  |  |  |

| Supply                                     | External                                                                                        |  |  |  |  |

| Fuse                                       | Required line fuse: Max. 32 A slow-blow (see "Overcurrent protection")                          |  |  |  |  |

| Output protection                          | Thermal shutdown in the event of overcurrent or short circuit                                   |  |  |  |  |

| Variant                                    | H bridge                                                                                        |  |  |  |  |

| Configurable dither                        | Amplitude, frequency                                                                            |  |  |  |  |

| Period duration resolution                 | 16-bit, min. 20 µs                                                                              |  |  |  |  |

| Phase shift PWM1, 2, 3, 4                  | 90° each                                                                                        |  |  |  |  |

| DC bus capacitance                         | 680 µF                                                                                          |  |  |  |  |

| PWM pulse width                            | ·                                                                                               |  |  |  |  |

| PWM mode                                   | 15 bits plus sign ≥10 ns                                                                        |  |  |  |  |

| Current mode                               | 15 bits plus sign ≥10 ns                                                                        |  |  |  |  |

| Insulation voltage between channel and bus | 500 V <sub>eff</sub>                                                                            |  |  |  |  |

| Electrical properties                      |                                                                                                 |  |  |  |  |

| Electrical isolation                       | Channel isolated from bus                                                                       |  |  |  |  |

|                                            | Channel not isolated from channel                                                               |  |  |  |  |

| Operating conditions                       |                                                                                                 |  |  |  |  |

| Mounting orientation                       |                                                                                                 |  |  |  |  |

| Horizontal                                 | Yes                                                                                             |  |  |  |  |

| Installation elevation above sea level     |                                                                                                 |  |  |  |  |

| 0 to 2000 m                                | No limitation                                                                                   |  |  |  |  |

| >2000 m                                    | Reduction of ambient temperature by 0.5°C per 100 m                                             |  |  |  |  |

| Degree of protection per EN 60529          | IP20                                                                                            |  |  |  |  |

| Ambient conditions                         |                                                                                                 |  |  |  |  |

| Temperature                                |                                                                                                 |  |  |  |  |

| Operation                                  |                                                                                                 |  |  |  |  |

| Horizontal mounting orientation            | 0 to 50°C                                                                                       |  |  |  |  |

| Vertical mounting orientation              | Not permitted                                                                                   |  |  |  |  |

| Derating                                   |                                                                                                 |  |  |  |  |

| Storage                                    | -25 to 70°C                                                                                     |  |  |  |  |

| Transport                                  | -25 to 70°C                                                                                     |  |  |  |  |

| Relative humidity                          |                                                                                                 |  |  |  |  |

| Operation                                  | 5 to 95%, non-condensing                                                                        |  |  |  |  |

| Storage                                    | 5 to 95%, non-condensing                                                                        |  |  |  |  |

| Transport                                  | 5 to 95%, non-condensing                                                                        |  |  |  |  |

| Mechanical properties                      |                                                                                                 |  |  |  |  |

| Note                                       | Order 2x terminal block X20TB12 separately.<br>Order 1x terminal block 0TB3103-7020 separately. |  |  |  |  |

| Pitch                                      | 87.5 <sup>+0.2</sup> mm                                                                         |  |  |  |  |

Table 2: X20MM4456 - Technical data

1) The tolerance value is composed of the voltage tolerances and permissible total AC voltage component with a peak value of 5% of the rated voltage.

# 4 LED status indicators

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" in the X20 system user's manual.

### Status LED, left

| Figure                                                                                                          | LED      | Color         | Status         | Description                                      |

|-----------------------------------------------------------------------------------------------------------------|----------|---------------|----------------|--------------------------------------------------|

|                                                                                                                 | r        | r Green Off   |                | No power to module                               |

|                                                                                                                 |          |               | Single flash   | RESET mode                                       |

| 1                                                                                                               |          |               | Double flash   | BOOT mode (during firmware update) <sup>1)</sup> |

| 0                                                                                                               |          |               | Blinking       | PREOPERATIONAL mode                              |

| ¥ 1 2                                                                                                           |          |               | On             | RUN mode                                         |

|                                                                                                                 | e Red    | Red           | Off            | No power to module or everything OK              |

| ž 5 6                                                                                                           |          |               | On             | Error or reset status                            |

| 8 7 5                                                                                                           | e+r      | Red on / Gree | n single flash | Invalid firmware                                 |

| × M2                                                                                                            | × M2 1-8 |               |                | Input state of the corresponding digital input   |

| The second se | M1 + M2  | Orange        | On             | The corresponding output is active               |

1) Depending on the configuration, a firmware update can take up to several minutes.

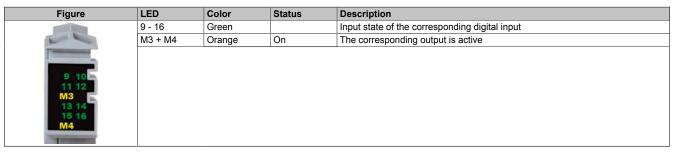

### Status LED, right

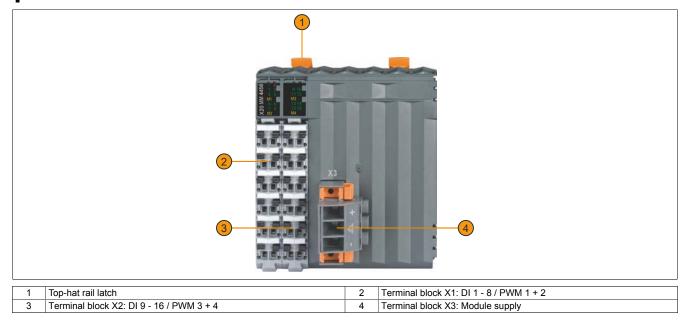

# **5** Connection elements

In accordance with the EN 60204-1 standard, a cable cross section of 1.5 mm<sup>2</sup> or larger must be used for the motor outputs in order to handle the maximum motor current of 10 A. To ensure full motor power, voltage drops that could result from the cable length and the electrical connections must also be taken into consideration when selecting the attachment cable.

# Warning!

The terminal block is not permitted to be plugged in or unplugged during operation.

# Information:

Shielded motor cables must be used in order to meet the limits according to the EN 55011 standard (emissions).

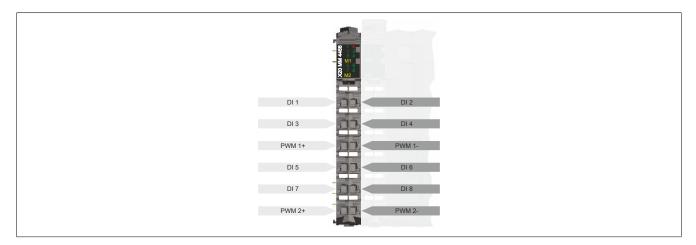

### 5.1 Terminal block X1 - DI 1 - 8 / PWM 1 + 2

### 5.2 Terminal block X2 - DI 9 - 16 / PWM 3 + 4

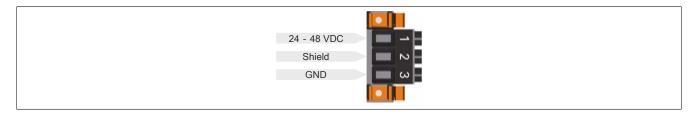

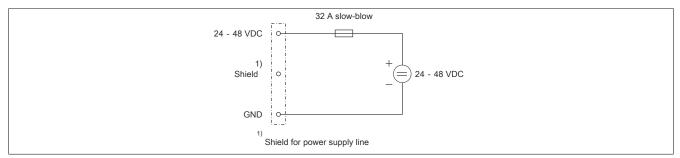

### 5.3 X3 terminal block - Module supply

# 6 Connection examples

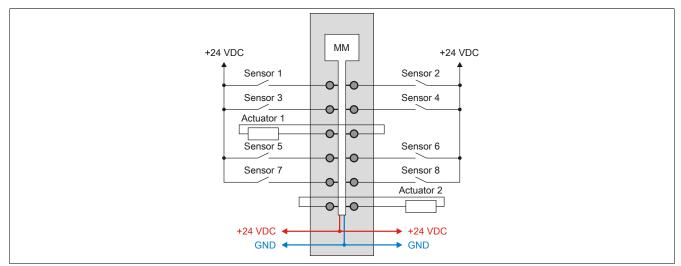

### X1 and X2 terminal blocks

The following image shows a connection example for the X1 terminal block. The connection example also applies to the X2 terminal block.

### X3 terminal block

For information on the fuse used, see "Protection" on page 8.

# 7 Possible uses for digital inputs

Digital input channels 1 to 16 can be used as follows:

| Channel | Function      | Special functions                       |

|---------|---------------|-----------------------------------------|

| DI 1    | Digital input | A                                       |

| DI 2    | Digital input | В                                       |

| DI 3    | Digital input | Limit switch, trigger, reference pulse  |

| DI 4    | Digital input | Limit switch, trigger, reference enable |

| DI 5    | Digital input | A                                       |

| DI 6    | Digital input | В                                       |

| DI 7    | Digital input | Limit switch, trigger, reference pulse  |

| DI 8    | Digital input | Limit switch, trigger, reference enable |

| DI 9    | Digital input | A                                       |

| DI 10   | Digital input | В                                       |

| DI 11   | Digital input | Limit switch, trigger, reference pulse  |

| DI 12   | Digital input | Limit switch, trigger, reference enable |

| DI 13   | Digital input | A                                       |

| DI 14   | Digital input | В                                       |

| DI 15   | Digital input | Limit switch, trigger, reference pulse  |

| DI 16   | Digital input | Limit switch, trigger, reference enable |

#### The functions can also be mixed:

| Example 1          |               |  |  |  |

|--------------------|---------------|--|--|--|

| Channel            | Function      |  |  |  |

| DI 1               | Digital input |  |  |  |

| DI 2               | Digital input |  |  |  |

| DI 3               | Digital input |  |  |  |

| DI 4               | Digital input |  |  |  |

| DI 5               | Digital input |  |  |  |

| DI 6               | Digital input |  |  |  |

| DI 7 Digital input |               |  |  |  |

| DI 8               | Digital input |  |  |  |

| DI 9               | A             |  |  |  |

| DI 10              | В             |  |  |  |

| DI 11              | R             |  |  |  |

| DI 12              |               |  |  |  |

| DI 13              | A             |  |  |  |

| DI 14              | В             |  |  |  |

| DI 15              | R             |  |  |  |

| DI 16              |               |  |  |  |

| Example 2           |               |  |  |  |

|---------------------|---------------|--|--|--|

| Channel             | Function      |  |  |  |

| DI 1                | A             |  |  |  |

| DI 2                | В             |  |  |  |

| DI 3                | R             |  |  |  |

| DI 4                |               |  |  |  |

| DI 5                | Digital input |  |  |  |

| DI 6                | Digital input |  |  |  |

| DI 7                | Digital input |  |  |  |

| DI 8                | Digital input |  |  |  |

| DI 8                | Digital input |  |  |  |

| DI 10 Digital input |               |  |  |  |

| DI 11 Digital input |               |  |  |  |

| DI 12               | Digital input |  |  |  |

| DI 13               | A             |  |  |  |

| DI 14               | В             |  |  |  |

| DI 15               | R             |  |  |  |

| DI 16               |               |  |  |  |

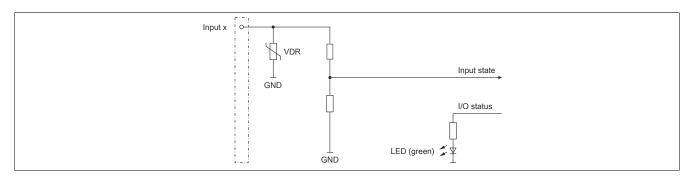

# 8 Input circuit diagram

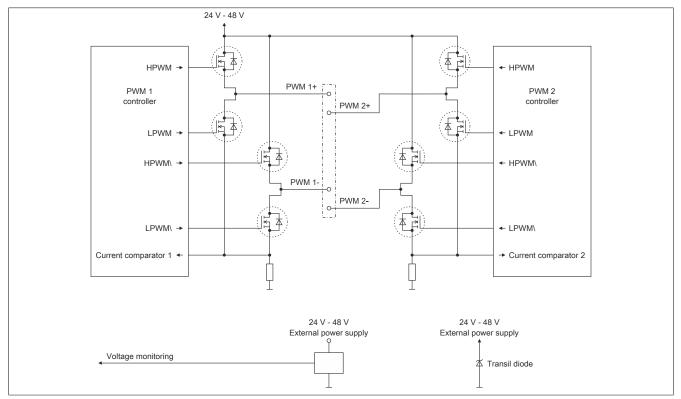

# 9 Output circuit diagram

The following image shows the output circuit diagram for the outputs 1 and 2. The diagram also applies to the outputs 3 and 4.

# **10 Protection**

The power supply line should be protected by a circuit breaker or a fuse. In general, dimensioning the supply line and overcurrent protection depends on the structure of the power supply (modules can be connected individually or in groups).

## Information:

The effective current for the power supply depends on the load, but is always less than the sum of the output currents. Make sure that the maximum nominal current of 31 A per pin is not exceeded on the power supply terminals of the power unit.

When choosing a suitable fuse, the user must also account for characteristics such as aging effects, temperature derating, overcurrent capacity and the definition of the rated current, which can vary by manufacturer and type. In addition, the fuse that is selected must also be able to handle application-specific characteristics (e.g. overcurrent that occurs in acceleration cycles).

The cross section of the power mains and the rated current of the overcurrent protection used are chosen according to the current load so that the maximum current load for the cable cross section selected (based on the type of layout, see table) is greater than or equal to the current load in the power mains. The rated current of the overcurrent protection must be less than or equal to the maximum current load for the cable cross section selected (based on the type of have) and the type of layout, see table):

| Mains                                 | ≤         | I <sub>b</sub> | ≤         | Iz                              |                                             |

|---------------------------------------|-----------|----------------|-----------|---------------------------------|---------------------------------------------|

| Mains                                 | ≤         | Fuse           | ≤         | Line/cable                      |                                             |

|                                       |           |                |           | rrent of the over current prote | ection I <sub>b</sub> [A] according to type |

| Wire cross section [mm <sup>2</sup> ] | B1        |                | B2        | C                               | E                                           |

| 1.5                                   | 13.5 / 13 |                | 13.1 / 10 | 15.2 / 13                       | 16.1 / 16                                   |

| 2.5                                   | 18.3 / 16 |                | 16.5 / 16 | 21 / 20                         | 22 / 20                                     |

| 4                                     | 24 / 24   |                | 23 / 20   | 28 / 25                         | 30 / 25                                     |

| 6                                     | 32 / 32   |                | 29 / 25   | 36 / 32                         | 37 / 32                                     |

Table 3: Cable cross section of the mains supply line depending on the type of layout

The tripping current of the fuse cannot exceed the rated current of fuse  $I_{b}$ .

| Type of layout | Description                        |

|----------------|------------------------------------|

| B1             | Wires in conduit or cable duct     |

| B2             | Cables in conduit or cable duct    |

| С              | Cables or wires on walls           |

| E              | Cables or wires on open cable tray |

Table 4: Type of layout for the mains supply line

# 11 Monitoring the module supply

The module supply is continually monitored. If the following limits are exceeded in either direction, an error bit is set.

| Upper limit:   | >80 V |

|----------------|-------|

| Warning stage: | >60 V |

| Lower limit:   | <18 V |

# 12 Overvoltage cutoff

If the supply voltage on the module exceeds 80V (e.g. through feedback during generator operation), then all PWM outputs are disabled (PWM output pins are short-circuited). The outputs are reactivated as soon as the supply voltage is back in the valid range. Switching the outputs on again can cause an open load error in current mode (depending on the current setpoint and load inductance) as well as with any other abrupt change to the current setpoint value.

# 13 Overtemperature cutoff (at 85°C)

If the module temperature reaches or exceeds the limit value of 85°C, then the module executes the following actions:

- Setting the "overtemperature" error bit

- The PWM outputs are disabled (short-circuited)

Once the module temperature sinks to 83°C, the error bit is automatically cleared by the module and the outputs become operational again.

# 14 Measurement of effective current

In current controller mode (see bit 12 in the "configuration register" on page 13), there is an apparent deviation between the current setpoint and the measured effective current.

This is due to how the module operates. The PWM output remains "On" or in "Fast Decay" as long as needed to reach the current setpoint. Therefore, the current setpoint is the maximum or minimum current in a specified PWM cycle. This is why the effective current of this cycle (average current of this cycle) is lower (PWM = "On") or higher (PWM = "Fast Decay") than the current setpoint.

The size of the deviation depends on the load impedance.

# 15 Derating

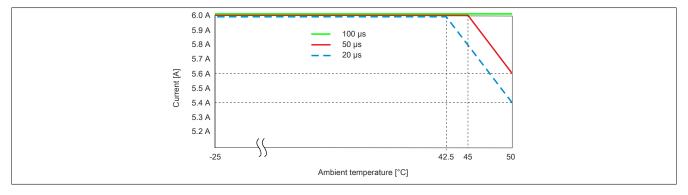

The temperature of the module is affected by the PWM period duration. The following derating must therefore be taken into account with a PWM period duration under  $100 \ \mu s$ .

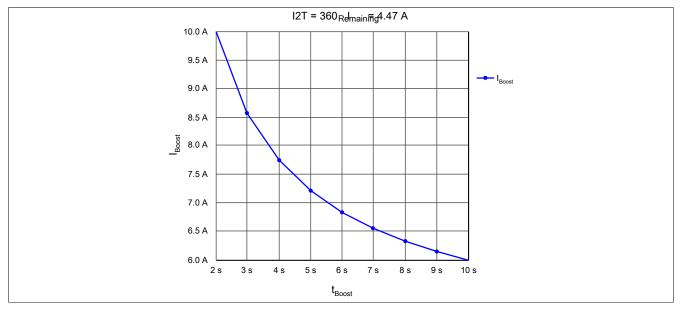

# 16 Let-through current I2T

The module is designed for let-through current of 360 A<sup>2</sup>s for a period of 10 seconds. If more current is needed for a certain time, less current must be drawn during the remaining time in order to maintain the let-through current.

### Calculating the remaining-time current

$$I_{\text{Boost}}^{2*} t_{\text{Boost}} + I_{\text{Remaining}}^{2*} \left( 10 - t_{\text{Boost}} \right) \le 360A^2 s$$

$$I_{\text{Remaining}} = \sqrt{\frac{360A^2 s - 1_{\text{Boost}}^{2*} t_{\text{Boost}}}{10s_{\circ} - t_{\text{Boost}}}}$$

### Example

A boost current of 8 A is needed for a duration of 3 seconds.

$$I_{\text{Remaining}} = \sqrt{\frac{360A^2 \,\text{s} - 8A^{2*} \,3\,\text{s}}{10\text{s} - 3\text{s}}} = 4.89A$$

| t <sub>Boost</sub> | IBoost | t <sub>Remaining</sub> | I <sub>Remaining</sub> | I2T                |

|--------------------|--------|------------------------|------------------------|--------------------|

| S                  | A      | S                      | A                      | A <sup>2</sup> * s |

| 10                 | 6.00   | 0                      | 0                      | 360.00             |

| 2                  | 10.00  | 8                      | 4.47                   | 360.00             |

| 3                  | 8.57   | 7                      | 4.47                   | 360.00             |

| 4                  | 7.75   | 6                      | 4.47                   | 360.00             |

| 5                  | 7.21   | 5                      | 5 4.47                 |                    |

| 6                  | 6.83   | 4                      | 4.47                   | 360.00             |

| 7                  | 6.55   | 3                      | 4.47                   | 360.00             |

| 8                  | 6.32   | 2                      | 4.47                   | 360.00             |

| 9                  | 6.15   | 1                      | 4.47                   | 360.00             |

These values correspond to the following curve for let-through current I2T:

# **17 Register description**

### 17.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X20 system user's manual.

### 17.2 Function model 0 - Standard

| Register           | Name                                                 | Data type | Re     | ad      | Write  |         |  |

|--------------------|------------------------------------------------------|-----------|--------|---------|--------|---------|--|

|                    |                                                      |           | Cyclic | Acyclic | Cyclic | Acyclic |  |

| Configuration      |                                                      |           |        |         |        |         |  |

| 64                 | ConfigOutput01                                       | USINT     |        |         |        | •       |  |

| 65                 | ConfigOutput02                                       | USINT     |        |         |        | •       |  |

| 72 + (N-1) * 8     | Configuration0N (index N = 1 to 4)                   | UINT      |        |         |        | •       |  |

| 74 + (N-1) * 8     | HoldingCurrent0N (index N = 1 to $4$ ) <sup>1)</sup> | INT       |        |         |        | •       |  |

| 76 + (N-1) * 8     | BoostCurrent0N (index N = 1 to $4$ ) <sup>1)</sup>   | INT       |        |         |        | •       |  |

| 78 + (N-1) * 8     | BoostTime0N (index N = 1 to 4) <sup>1)</sup>         | UINT      |        |         |        | •       |  |

| 104 +<br>(N-1) * 2 | SwitchingPeriod0N (index N = 1 to 4) <sup>1)</sup>   | UINT      |        |         |        | •       |  |

| Communicatio       | on                                                   |           |        |         | 1      |         |  |

| 0 + (N-1) * 8      | PulseWidthCurrentPWM0N (index N = 1 to 4)            | INT       |        |         | •      |         |  |

| 0 + (N-1) * 8      | Counter0N (index N = 1 to 4)                         | INT       | •      |         |        |         |  |

| 2 + (N-1) * 8      | CounterLatch0N (index N = 1 to 4)                    | INT       | •      |         |        |         |  |

| 2 + (N-1) * 8      | Control                                              | USINT     |        |         | •      |         |  |

| . , -              | TriggerEdge0N                                        | Bit 0     |        |         |        | 1       |  |

|                    | StartTrigger0N                                       | Bit 1     |        |         |        |         |  |

|                    | StartLatch0N                                         | Bit 2     |        |         |        |         |  |

|                    | DitherDisable0N                                      | Bit 3     |        |         |        |         |  |

|                    | ClearError0N                                         | Bit 4     |        |         |        |         |  |

|                    | ShowMeanCurrent0N                                    | Bit 5     |        |         |        |         |  |

|                    | ResetCounter0N                                       | Bit 6     |        |         |        |         |  |

|                    | OutputEnable0N                                       | Bit 7     |        |         |        |         |  |

| 4                  | PeriodDurationPWM                                    | UINT      |        |         | •      |         |  |

| 4 + (N-1) * 8      | usSinceTrigger0N (index N = 1 to 4)                  | UINT      | •      |         |        |         |  |

| 6 + (N-1) * 8      | Status0N (index N = 1 to 4)                          | USINT     | •      |         |        |         |  |

| ( )                | StatusInput(N-1)*4 + 1                               | Bit 0     |        |         |        |         |  |

|                    |                                                      |           |        |         |        |         |  |

|                    | StatusInput(N-1)*4 + 4                               | Bit 3     |        |         |        |         |  |

|                    | nLatchPending0N                                      | Bit 4     |        |         |        |         |  |

|                    | LatchDone0N                                          | Bit 5     |        |         |        |         |  |

|                    | EndswitchReached0N                                   | Bit 6     |        |         |        |         |  |

|                    | PWMError0N                                           | Bit 7     |        |         |        |         |  |

| 7                  | Global error                                         | USINT     | •      |         |        |         |  |

|                    | OverVoltageError                                     | Bit 4     |        |         |        | 1       |  |

|                    | UnderVoltageError                                    | Bit 5     |        |         |        |         |  |

|                    | VoltageWarning                                       | Bit 6     |        |         |        |         |  |

|                    | OvertemperatureError                                 | Bit 7     |        |         |        |         |  |

| 15                 | Channel errors                                       | USINT     | •      |         |        |         |  |

|                    | CurrentError01                                       | Bit 0     |        |         |        | 1       |  |

|                    | OverCurrentError01                                   | Bit 1     |        |         |        |         |  |

|                    | CurrentError02                                       | Bit 2     |        |         |        |         |  |

|                    | OverCurrentError02                                   | Bit 3     |        |         |        |         |  |

|                    | CurrentError03                                       | Bit 4     |        |         |        |         |  |

|                    | OverCurrentError03                                   | Bit 5     |        |         |        |         |  |

|                    | CurrentError04                                       | Bit 6     |        |         |        |         |  |

|                    | OverCurrentError04                                   | Bit 7     |        |         |        |         |  |

| 128                | ModuleTemperature                                    | SINT      |        | •       |        | 1       |  |

1) Only available with firmware version 102 or later

### 17.3 Function model 254 - Bus controller

| Register                     | Offset <sup>1)</sup>         | Name                                                        | Data type       | Re     | ad      | W      | rite    |

|------------------------------|------------------------------|-------------------------------------------------------------|-----------------|--------|---------|--------|---------|

|                              |                              |                                                             |                 | Cyclic | Acyclic | Cyclic | Acyclic |

| Configuration                |                              |                                                             |                 |        |         |        |         |

| 64                           | -                            | ConfigOutput01                                              | USINT           |        |         |        | •       |

| 65                           | -                            | ConfigOutput02                                              | USINT           |        |         |        | •       |

| 72 + (N-1) * 8               | -                            | Configuration0N (index N = 1 to 4)                          | UINT            |        |         |        | •       |

| 74 + (N-1) * 8               | -                            | HoldingCurrent0N (index N = 1 to 4)                         | INT             |        |         |        | •       |

| 76 + (N-1) * 8               | -                            | BoostCurrent0N (index N = 1 to 4)                           | INT             |        |         |        | •       |

| 78 + (N-1) * 8               | -                            | BoostTime0N (index N = 1 to 4)                              | UINT            |        |         |        | •       |

| 104 +<br>(N-1) * 2           | -                            | SwitchingPeriod0N (index N = 1 to 4)                        | UINT            |        |         |        | •       |

| Communicatio                 |                              |                                                             |                 |        | 1       |        | 1       |

| 0 + (N-1) * 8                | 0 + (N-1) * 8                |                                                             | INT             |        |         | •      |         |

| 0 + (N-1) * 8                | 0 + (N-1) * 8                |                                                             | INT             | •      |         |        |         |

| 2 + (N-1) * 8                | 2 + (N-1) * 8                |                                                             | INT             | •      |         |        |         |

| 2 + (N-1) * 8                | 2 + (N-1) * 8                | Control                                                     | USINT           |        |         | •      |         |

|                              |                              | TriggerEdge0N                                               | Bit 0           |        |         |        |         |

|                              |                              | StartTrigger0N                                              | Bit 1           |        |         |        |         |

|                              |                              | StartLatch0N                                                | Bit 2           |        |         |        |         |

|                              |                              | DitherDisable0N                                             | Bit 3           |        |         |        |         |

|                              |                              | ClearError0N                                                | Bit 4           |        |         |        |         |

|                              |                              | ShowMeanCurrent0N                                           | Bit 5           |        |         |        |         |

|                              |                              | ResetCounter0N                                              | Bit 6           |        |         |        |         |

| 4                            | 4                            | OutputEnable0N<br>PeriodDurationPWM                         | Bit 7<br>UINT   |        |         |        |         |

|                              | -                            |                                                             | UINT            |        |         | •      |         |

| 4 + (N-1) * 8<br>6 (N-1) * 8 | 4 + (N-1) * 8<br>6 (N-1) * 8 | usSinceTrigger0N (index N = 1 to 4)<br>Status of the inputs | UINT<br>U(S)INT | •      |         |        |         |

| 0(11-1) 0                    | 0(11-1) 0                    | Status of the liputs<br>StatusInput(N-1) * 4 + 1            | Bit 0           | •      |         |        |         |

|                              |                              |                                                             |                 |        |         |        |         |

|                              |                              | StatusInput(N-1) * 4 + 4                                    | <br>Bit 3       |        |         |        |         |

|                              |                              | nLatchPending0N                                             | Bit 4           |        |         |        |         |

|                              |                              | LatchDone0N                                                 | Bit 5           |        |         |        |         |

|                              |                              | EndswitchReached0N                                          | Bit 6           |        |         |        |         |

|                              |                              | PWMError0N                                                  | Bit 7           |        |         |        |         |

|                              |                              | CurrentError01                                              | Bit 8           |        |         |        |         |

|                              |                              | OverCurrentError01                                          | Bit 9           |        |         |        |         |

|                              |                              | CurrentError02                                              | Bit 10          |        |         |        |         |

|                              |                              | OverCurrentError02                                          | Bit 11          |        |         |        |         |

|                              |                              | CurrentError03<br>OverVoltageError                          | Bit 12          |        |         |        |         |

|                              |                              | OverCurrentError03<br>UnderVoltageError                     | Bit 13          |        |         |        |         |

|                              |                              | CurrentError04<br>VoltageWarning                            | Bit 14          |        |         |        |         |

|                              |                              | OverCurrentError04<br>OvertemperatureError                  | Bit 15          |        |         |        |         |

| 128                          | -                            | ModuleTemperature                                           | SINT            |        | •       |        |         |

1) The offset specifies the position of the register within the CAN object.

#### 17.3.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X20 user's manual (version 3.50 or later).

#### 17.3.2 CAN I/O bus controller

The module occupies 4 analog logical slots on CAN I/O.

# 17.4 Configuration

### 17.4.1 Configuration

#### Name:

Configuration01 to Configuration04

These registers can be used to configure the 4 DC motors.

### The following placeholders are used in the configuration table:

| Register        | Channel                | N | In1             | In2  |

|-----------------|------------------------|---|-----------------|------|

| Configuration01 | 1                      |   | DI3             | DI4  |

| Configuration02 | 2                      |   | DI7             | DI8  |

| Configuration03 | 3                      |   | DI11            | DI12 |

| Configuration04 | 4                      |   | DI15            | DI16 |

| Data type       | Values Bus controlle   |   | default setting |      |

| UINT            | See the bit structure. | 0 |                 |      |

#### Bit structure:

| Bit     | Description                                                             | Value   | Information                                                                                                                 |

|---------|-------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------|

| 0 - 1   | Configuration of the latch function for ABR counter <b>N</b> . Enabling | 00      | ABR counter <b>N</b> is latched unconditionally (default setting). The                                                      |

|         | he latch function is described in the control register (bit 2):         |         | reference enable input is ignored (bus controller default setting).                                                         |

|         |                                                                         | 01      | ABR counter <b>N</b> is latched if a rising edge occurs on digital input                                                    |

|         |                                                                         |         | <b>In1</b> and reference enable input <b>In2</b> is "1". The reference enable input must be enabled to do this (see bit 2). |

|         |                                                                         | 10      | ABR counter <b>N</b> is latched if a falling edge occurs on digital input                                                   |

|         |                                                                         | 10      | <b>In1</b> and reference enable input <b>In2</b> is "1". The reference enable                                               |

|         |                                                                         |         | input must be enabled to do this (see bit 2).                                                                               |

|         |                                                                         | 11      | The latch function is disabled.                                                                                             |

| 2       | Reference enable input:                                                 | 0       | No reference enable input (bus controller default setting)                                                                  |

|         |                                                                         | 1       | Digital input In2 is used as the reference enable input.                                                                    |

| 3       | Active level of the reference enable input for ABR counter N:           | 0       | Active level = High (bus controller default setting)                                                                        |

|         |                                                                         | 1       | Active level = Low                                                                                                          |

| 4       | Reserved                                                                | 0       |                                                                                                                             |

| 5 - 7   | Definition of the limit switch N (see also "Limit switch function"      | 000     | Limit switch N is disabled (bus controller default setting)                                                                 |

|         | on page 14):                                                            | 001     | Digital input In1 is used as the Enable input.1)                                                                            |

|         |                                                                         | 010     | Digital input In1 is used as the limit switch.                                                                              |

|         |                                                                         | 011     | Reserved                                                                                                                    |

|         |                                                                         | 100     | Digital input <b>In2</b> is used as the limit switch.                                                                       |

|         |                                                                         | 101     | Reserved                                                                                                                    |

|         |                                                                         | 110     | Digital inputs In1 and In2 are used as the left and right limit                                                             |

|         |                                                                         |         | switches.                                                                                                                   |

|         |                                                                         | 111     | Reserved                                                                                                                    |

| 8       | Active level for limit switch N:                                        | 0       | Active level = High (bus controller default setting)                                                                        |

|         |                                                                         | 1       | Active level = Low                                                                                                          |

| 9 - 10  | Trigger input for trigger counter "usSinceTrigger" N:                   | 00      | The trigger counter is disabled (bus controller default setting).                                                           |

|         |                                                                         | 01      | Digital input In1 is used as the trigger input.                                                                             |

|         |                                                                         | 10      | Digital input <b>In2</b> is used as the trigger input.                                                                      |

|         |                                                                         | 11      | Reserved                                                                                                                    |

| 11      | Display of current average for output N:                                | 0       | If the corresponding setting has been enabled, then the average                                                             |

|         |                                                                         |         | current value is indicated in register "CounterLatch[x]" on page 20 (see bit 5 in the "control register" on page 14) (bus   |

|         |                                                                         |         | controller default setting)                                                                                                 |

|         |                                                                         | 1       | If the corresponding setting has been enabled, then the average                                                             |

|         |                                                                         |         | current value is indicated in register "usSinceTrigger[x]" on page                                                          |

|         |                                                                         |         | 21 (see bit 5 in the "control register" on page 14).                                                                        |

| 12 + 15 | Output mode N:                                                          | 00      | PWM mode (bus controller default setting)                                                                                   |

|         |                                                                         | 01      | Current mode                                                                                                                |

|         |                                                                         | 10      | Boost-and-hold current control <sup>1)</sup>                                                                                |

|         |                                                                         | 11      | Reserved                                                                                                                    |

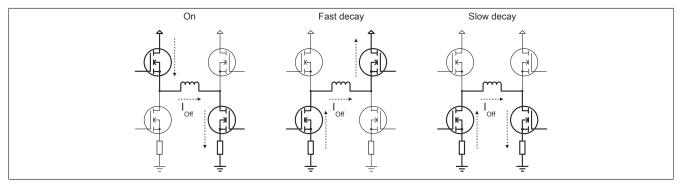

| 13 - 14 | Decay configuration for PWM N (see also "Decay configura-               | 00      | Slow decay (bus controller default setting)                                                                                 |

|         | tion" on page 24):                                                      | 01      | Mixed decay                                                                                                                 |

|         |                                                                         | 10 - 11 | Reserved                                                                                                                    |

1) Only available with firmware version 102 or later

### Limit switch function

The limit switch function serves to quickly shut off the PWM outputs when a limit position is reached.

The limit switch is activated and the disable edge (rising or falling) on the limit switch input is selected using bits 6 to 8.

A PWM output is disabled as soon as the configured disable edge is reached on the corresponding input of the limit switch. This cutoff occurs independently of the current direction of movement. It remains disabled until either the limit switch function is disabled or the limit switch is acknowledged with bit 4 in the corresponding "control register" on page 14.

#### Enable input

The limit switch input of the module can optionally be used as an enable input. Bits 5 to 7 must be configured accordingly for this. Data point OutputEnable and the digital input are logically linked by an AND operator.

When the enable input is enabled, the PWM output can be switched on and off via the digital input. Switching on and off is done with a jitter of 50  $\mu$ s. Since it is possible to react only at the beginning of the PWM period, an additional jitter of the length of the PWM period duration must be taken into account.

#### 17.4.2 Control

Name:

TriggerEdge01 to TriggerEdge04 StartTrigger01 to StartTrigger04 StartLatch01 to StartLatch04 DitherDisable01 to DitherDisable04 ClearError01 to ClearError04 ShowMeanCurrent01 to ShowMeanCurrent04 ResetCounter01 to ResetCounter04 OutputEnable01 to OutputEnable04

These registers can be used to configure the behavior of the trigger, the ABR counter and the dither.

[N] stands for the index number of the register.

| Data type | Values                 |

|-----------|------------------------|

| USINT     | See the bit structure. |

#### Bit structure:

| Bit | Description                                                                   | Value | Information                                                                                                                                                    |

|-----|-------------------------------------------------------------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TriggerEdgeN                                                                  | 0     | Counting starts at rising edge                                                                                                                                 |

|     | Configuration of trigger edge for "usSinceTrigger":                           | 1     | Counting starts at falling edge                                                                                                                                |

| 1   | StartTriggerN<br>Enabling of "usSinceTrigger" due to a status change of bit 1 | x     | Counting starts at the next trigger edge (see bit 0). For more in-<br>formation about trigger functionality, see "Trigger function pro-<br>cedure" on page 15. |

| 2   | StartLatchN                                                                   | 0     | Disabled                                                                                                                                                       |

|     | Latching or referencing ABR counters:                                         | 1     | Enabled                                                                                                                                                        |

| 3   | DitherDisable N                                                               | 0     | Dither for PWM output <b>N</b> is switched on. The dither frequency<br>and dither amplitude must be greater than 0 (see "Dither" on<br>page 18).               |

|     |                                                                               | 1     | Dither for PWM output N is switched off.                                                                                                                       |

| 4   | ClearErrorN                                                                   | 0     | No effect                                                                                                                                                      |

|     | Acknowledging error or limit switch:                                          | 1     | Error acknowledgment on output N (overcurrent or open load)<br>or acknowledgment of limit switch N                                                             |

| 5   | ShowMeanCurrentN<br>Konfiguration der Register "CounterLatch" on page 20 und  | 0     | Register CounterLatchN contains the latched counter value.<br>Register usSinceTriggerN contains the trigger counter.                                           |

|     | "usSinceTrigger" on page 21                                                   | 1     | Both registers contain the current PWM output current                                                                                                          |

| 6   | ResetCounterN                                                                 | 0     | Enable ABR counter                                                                                                                                             |

|     | Reset ABR counter                                                             | 1     | Reset ABR counter                                                                                                                                              |

| 7   | OutputEnableN <sup>1)</sup>                                                   | 0     | Switch off the PWM output                                                                                                                                      |

|     |                                                                               | 1     | Switch on the PWM output                                                                                                                                       |

1) Only for boost-and-hold current control.

### **Trigger function procedure**

The following points must be taken into consideration when configuring or activating the trigger function:

- Select the desired trigger edge using bit 0

- Enable the trigger function by changing the state of StartTrigger (bit 1). This edge clears the register usSinceTrigger (μs counter).

- When the trigger event occurs, the µs counter "usSinceTrigger" is started

- The "usSinceTrigger" counter cannot overrun, i.e. the counter is stopped at 2<sup>16</sup>-1 and retains this value until the next time the trigger function is activated

- The trigger function can be re-activated at any time by changing the state of StartTrigger (bit 1) regardless of if a trigger event has occurred or if "usSinceTrigger" has reached its maximum value.

### **Reset ABR counter**

Bit 6 sets the following counters and status bits to 0:

- ABR counter

- · Latch value of the ABR counter

- Latching started on the ABR counter (bit 4 of the "status register" on page 22)

- ABR counter successfully latched (bit 5 of the "status register" on page 22)

Please note that a started latch procedure is no longer active after the ABR counter has been reset. This means that latching must be restarted by a rising edge on bit 2.

### OutputEnable

Bit 7 can start or stop the output profile in Boost-and-hold current control. If a rising edge occurs on this data point, any pending Overcurrent error or Open load error of the associated PWM output are acknowledged and the output is switched on.

Starting or stopping occurs immediately after the transfer of the value on the X2X Link network with a jitter of 50  $\mu$ s. Note that during startup, an additional jitter of the length of the PWM period duration of the current controller is added.

Starting and stopping the output profile can also be controlled by the digital input. See "Enable input" on page 14.

#### 17.4.3 Difference between operating modes

The module provides the following operating modes:

- PWM mode

- Current mode

- Boost-and-hold current control

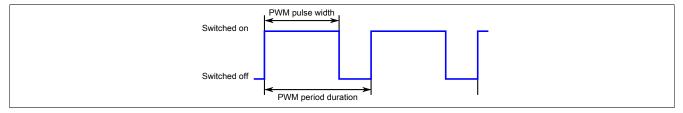

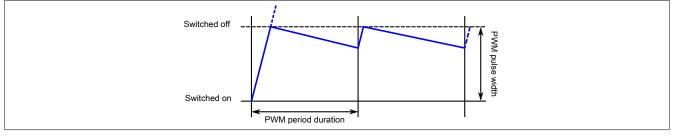

The following graphics show how the voltage or current curve of the outputs is affected by registers "PWM period duration" on page 20 and "PWM pulse width" on page 20.

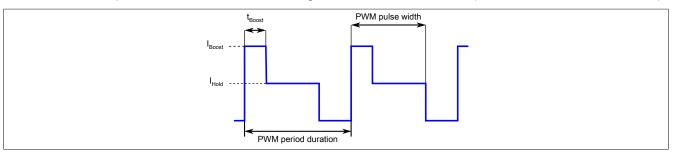

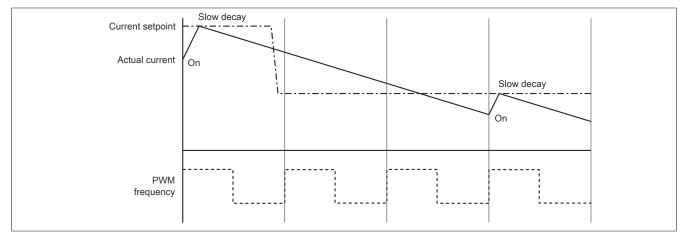

#### PWM mode

At the beginning of each period, the output is switched on for the percentage of time set in the PWM pulse width.

Figure 1: Voltage curve during PWM mode

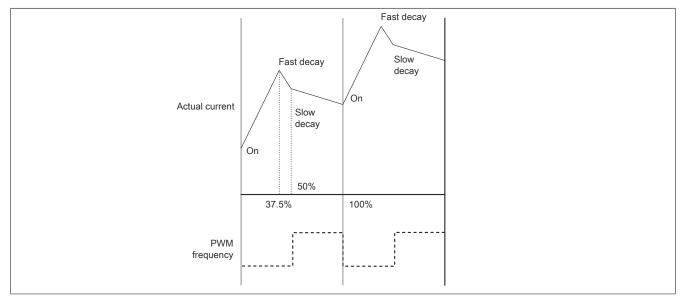

### Current mode

At the beginning of each period, the current output is switched on. After reaching the value set in "PulseWidthCurrentPWM" on page 20, the output is switched off and the voltage drops according to the set decay configuration until it is next switched on.

Figure 2: Current curve during current mode

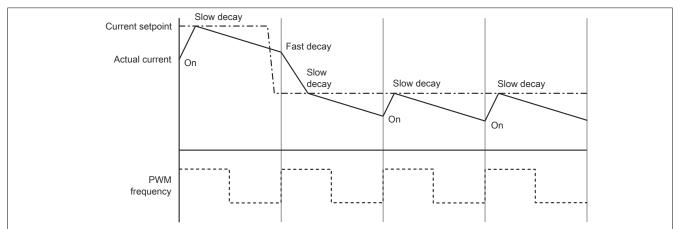

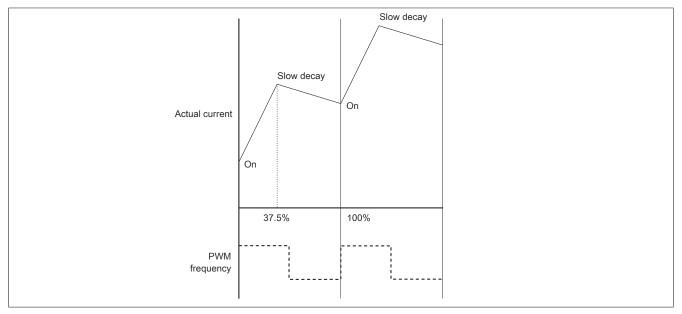

### **Boost-and-hold current control**

# Information:

#### Only available with firmware version 102 or later.

In this operating mode, the current mode is combined with a higher-level PWM mode.

After the time ( $t_{Boost}$ ) set in register "BoostTime" on page 17, the inrush current ( $I_{Boost}$ ) is changed to the holding current ( $I_{Holding}$ ) specified in register "HoldingCurrent" on page 17.

The period duration of the current profile is set in register "SwitchingPeriod" on page 17 in 50-µs steps. In addition, the PWM period duration must be set in register PeriodDurationPWM. (Not shown, see Current mode.)

Figure 3: Current curve during boost-and-hold mode

#### 17.4.3.1 Example: Controlling a digital valve

The boost current ( $I_{Boost}$ ) is used to quickly open a digital valve, for example. After the boost time ( $t_{Boost}$ ), the current is reduced to the lower holding current ( $I_{Holding}$ ) in order to save energy and not overload the PWM output.  $I_{Holding}$  is therefore set to a smaller value than  $I_{Boost}$ .

The pulse width can be used to set the opening time of the valve in relation to the period duration. After the period duration has expired,  $I_{Boost}$  is started again. If the valve should remain open continuously, the pulse width must be set to 100%. In this case, no boost current is output at the beginning of the next period.

$I_{Boost}$  is only output if the valve has been switched off for at least 50 µs. If the pulse width is set smaller than  $t_{Boost}$ , the boost time is shortened accordingly.

### 17.4.4 Boost-and-hold registers

#### 17.4.4.1 Boost current

Name: BoostCurrent01 to BoostCurrent04

The boost current is set in mA in this register.

| Data type | Values     | Information   |

|-----------|------------|---------------|

| INT       | 0 to 10000 | For 0 to 10 A |

### 17.4.4.2 Boost time

Name:

BoostTime01 to BoostTime04

The sampling time is set in µs in this register. The entered value is rounded up to the next largest 50-µs interval.

| Data type | Values     | Information |

|-----------|------------|-------------|

| UINT      | 0 to 65500 | In µs       |

#### 17.4.4.3 Holding current

Name:

HoldingCurrent01 to HoldingCurrent04

The holding current is set in mA in this register. After the boost time, the current for the remaining pulse width time is raised or lowered to this value.

| Data type | Values    | Information  |

|-----------|-----------|--------------|

| INT       | 0 to 6000 | For 0 to 6 A |

#### 17.4.4.4 Period duration of the current profile

Name:

SwitchingPeriod01 to SwitchingPeriod04

This register is used to set the period duration of the current profile in  $\mu$ s for boost-and-hold mode. The entered value is rounded up to the next largest 50- $\mu$ s interval.

| Data type | Values        | Information                    |

|-----------|---------------|--------------------------------|

| UINT      | 2000 to 65500 | Corresponds to 500 to 15.26 Hz |

#### 17.4.4.5 Synchronous operation of channels

In order for 2 or more channels to run synchronously, their period durations of the output profile (SwitchingPeriod) must be set to the same value or to a multiple of the other channel. An exact phase position of 0 degrees can only be guaranteed if the channels are switched on simultaneously (in the same bus cycle) with OutputEnable.

To operate the current profile synchronously to the X2X Link network, SwitchingPeriod should be set to a multiple of the bus cycle.

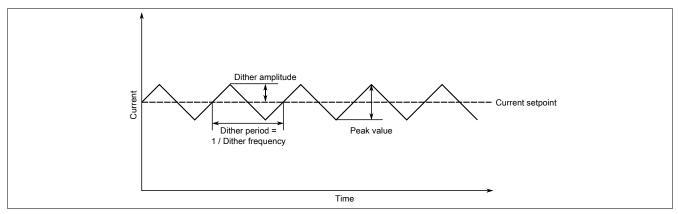

#### 17.4.5 Dither

When the position setpoint for valves remains constant for a long period of time, especially in fluids, there is a risk that a valve will stick. This is normally prevented using "dithering". When doing so, the value is permitted to slightly oscillate around the position setpoint.

By default, the dither is active for both outputs as soon as the dither amplitude and dither frequency are set to a value >0. If necessary, the dither can be disabled for each output individually or simultaneously (see bit 3 in register "control register" on page 14).

No dither is used in boost-and-hold mode of the PWM output. Any set dither amplitude and dither frequency are ignored by the module.

#### 17.4.5.1 Dither amplitude

Name: ConfigOutput01

This register can be used to configure the amplitude value or pulse width.

| Data type | Value    | Information                                                            |  |

|-----------|----------|------------------------------------------------------------------------|--|

| USINT     | 0 to 255 | Current mode: 0 to 25.5% of the module's nominal current <sup>1)</sup> |  |

|           |          | PWM mode: 0 to 25.5% of the period duration.                           |  |

|           |          | Bus controller default setting: 0                                      |  |

1) See the technical data for the module.

#### 17.4.5.2 Dither frequency

Name: ConfigOutput02

This register can be used to set the frequency in 2 Hz steps.

| Data type | Value    | Information                       |

|-----------|----------|-----------------------------------|

| USINT     | 0 to 255 | Corresponds to 0 to 510 Hz.       |

|           |          | Bus controller default setting: 0 |

#### 17.4.5.3 Dither example

The values specified in the data sheet for a valve should be used to calculate Dither amplitude and Dither frequency.

#### Data sheet for the valve

The data sheet for a valve manufacturer recommends the following dithering:

Dither height in percent (A<sub>Dither</sub>): 20 to 35% (peak values) of the nominal valve current of 2 A

Dither frequency in Hertz (F<sub>Dither</sub>): 40 to 70 Hz

#### **Selected values**

These values correspond to the average values on the valve data sheet.

A<sub>Dither</sub> = 27% of the valve's nominal current (peak values)

F<sub>Dither</sub> = 56 Hz

#### Formulas

Dither amplitude =  $(A_{Dither} / 2) * (Nominal current_{Valve} / Nominal current_{Module}) * 10$ Info:  $(A_{Dither} / 2)$  = Conversion of the peak values to amplitude, " \* 10" = Scaling of the dither amplitude to 1/10%

Dither frequency =  $F_{Dither}$  / 2 Hz Info: Dither frequency is configured in 2 Hz steps.

#### Calculation

By using the selected values in the formulas.

Dither amplitude = 27% / 2 \* (2 A / 6 A) \* 10 = 45

Dither frequency = 56 Hz / 2 Hz = 28

### 17.5 Communication

#### 17.5.1 PWM pulse width

Name:

PulseWidthCurrentPWM01 to PulseWidthCurrentPWM04

The PWM pulse width (PWM mode) or current setting (in current mode) is specified in this register according to the setting in the module configuration register (see also "Difference between operating modes" on page 16). A negative value changes the output polarity.

#### **PWM mode**

| Data type | Value  | Output +                             | Output -                             |

|-----------|--------|--------------------------------------|--------------------------------------|

| INT       | 32767  | High                                 | Low                                  |

|           | 16384  | PWM 50/50                            | Low                                  |

|           | 0      | Low (bus controller default setting) | Low (bus controller default setting) |

|           | -16384 | Low                                  | PWM 50/50                            |

|           | -32767 | Low                                  | High                                 |

#### Current mode

| Data type | Value            | Current mode           |

|-----------|------------------|------------------------|

| INT       | 19661 to 32767   | 6 to 10 A (max. 2 s)   |

|           | 19660            | 6 A                    |

|           | 0                | 0 A                    |

|           | -19660           | -6 A                   |

|           | -19661 to -32767 | -6 to -10 A (max. 2 s) |

#### **Boost-and-hold current control**

In this operating mode, this register is used to control the pulse width of the output signal in a way similar to PWM mode. In contrast, the pulse width of the current profile is specified. See "Current mode" on page 16.

In this operating mode, the pulse width can be set with a resolution of 50 µs. The pulse width of the current is specified as a percentage of the period duration of output signal SwitchingPeriod. If the value of this register is modified during a period, the pulse width is immediately adjusted.

Negative values correspond to an output with negative current direction.

| Data type | Values          | Information       |

|-----------|-----------------|-------------------|

| INT       | -32768 to 32767 | For -100% to 100% |

#### 17.5.2 PWM period duration

Name: PeriodDurationPWM

| Data type | Value       | Information |

|-----------|-------------|-------------|

| UINT      | 20 to 65535 | Time in µs  |

#### 17.5.3 ABR counter

Name:

Counter01 to Counter04

These registers are 16-bit AB(R) counters.

| Data type | Values          |

|-----------|-----------------|

| INT       | -32768 to 32767 |

#### 17.5.4 ABR counter latch

Name:

CounterLatch01 to CounterLatch04

When a latch event occurs, the current counter values are saved in these registers. For additional features, see bit 5 in the respective "control register" on page 14.

| Data type | Values          |

|-----------|-----------------|

| INT       | -32768 to 32767 |

#### 17.5.5 Microseconds since trigger

Name:

usSinceTrigger01 to usSinceTrigger04

This register shows either the time in µs since the last trigger event or the average current value.

### Counting mode