# X67IF1121-1

# **1** General information

Serial interfaces (barcode scanners for example) are often scattered throughout systems. This interface module from the remote X67 system is the optimal choice for this area of application: RS232 and RS485/RS422 connection options directly where they are needed, distributed on the machine or system.

In addition, there are digital inputs and outputs on the same module so that corresponding 24 V sensors/actuators can also be connected.

- RS232 and RS485/RS422 usable in parallel

- 2 digital channels, configurable as inputs or outputs

- 2 digital inputs

- Connection of barcode readers, ID systems and sensors on one module

# 1.1 Other applicable documents

For additional and supplementary information, see the following documents.

#### Other applicable documents

| Document name | Title                    |

|---------------|--------------------------|

| MAX67         | X67 system user's manual |

| MAEMV         | Installation / EMC guide |

# 2 Order data

| Order number | Short description                                                                                                                                                                                                              | Figure |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|              | Communication modules                                                                                                                                                                                                          |        |

| X67IF1121-1  | X67 interface module, 1 RS232 interface, 1 RS422/485 inter-<br>face, 2 digital channels configurable as inputs or outputs, 24<br>VDC, 0.5 A, configurable input filter, 2 inputs, 24 VDC, sink, con-<br>figurable input filter |        |

Table 1: X67IF1121-1 - Order data

#### **Required accessories**

For a general overview, see section "Accessories - General overview" of the X67 system user's manual.

# **3 Technical description**

# 3.1 Technical data

| Order number                                               | X67IF1121-1                                                                                                            |

|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Short description                                          |                                                                                                                        |

| Communication module                                       | 1x RS232 or 1x RS485/RS422, 2 digital inputs, 2 digi-<br>tal channels configurable as inputs or outputs using software |

| General information                                        |                                                                                                                        |

| Insulation voltage between channel and bus                 | 500 V <sub>eff</sub>                                                                                                   |

| B&R ID code                                                | 0xA90F                                                                                                                 |

| Sensor/Actuator power supply                               | 0.5 A summation current                                                                                                |

| Status indicators                                          | RS232, RS485/RS422, I/O function per channel, supply voltage, bus function                                             |

| Diagnostics                                                |                                                                                                                        |

| Outputs                                                    | Yes, using LED status indicator and software                                                                           |

| I/O power supply                                           | Yes, using LED status indicator and software                                                                           |

| RS232                                                      | Yes, using LED status indicator                                                                                        |

| RS485/RS422                                                | Yes, using LED status indicator                                                                                        |

| Connection type                                            |                                                                                                                        |

| X2X Link                                                   | M12, B-coded                                                                                                           |

| Interfaces and inputs/outputs                              | 4x M12, A-coded                                                                                                        |

| I/O power supply                                           | M8, 4-pin                                                                                                              |

| Power consumption                                          |                                                                                                                        |

| Internal I/O                                               | 2.4 W                                                                                                                  |

| X2X Link power supply                                      | 0.75 W                                                                                                                 |

| Certifications                                             |                                                                                                                        |

| CE                                                         | Yes                                                                                                                    |

| ATEX                                                       | Zone 2, II 3G Ex nA IIA T5 Gc<br>IP67, Ta = 0 - Max. 60°C<br>TÜV 05 ATEX 7201X                                         |

| UL                                                         | cULus E115267<br>Industrial control equipment                                                                          |

| HazLoc                                                     | cCSAus 244665<br>Process control equipment<br>for hazardous locations<br>Class I, Division 2, Groups ABCD, T5          |

| EAC                                                        | Yes                                                                                                                    |

| KC                                                         | Yes                                                                                                                    |

| Interfaces                                                 |                                                                                                                        |

| Interface IF1                                              |                                                                                                                        |

| Signal                                                     | RS232                                                                                                                  |

| Max. distance                                              | 900 m                                                                                                                  |

| Transfer rate                                              | Max. 115.2 kbit/s                                                                                                      |

| FIFO buffer                                                | Software                                                                                                               |

| Handshake lines                                            | No                                                                                                                     |

| Interface IF2                                              |                                                                                                                        |

| Signal                                                     | RS485/RS422                                                                                                            |

| Max. distance                                              | 1200 m                                                                                                                 |

| Transfer rate                                              | Max. 115.2 kbit/s                                                                                                      |

| FIFO buffer                                                | Software                                                                                                               |

| Terminating resistor                                       | Integrated in module                                                                                                   |

| I/O power supply                                           |                                                                                                                        |

| Nominal voltage                                            | 24 VDC                                                                                                                 |

| Voltage range                                              | 18 to 30 VDC                                                                                                           |

| Integrated protection                                      | Reverse polarity protection                                                                                            |

| Power consumption                                          | May 40 W/b                                                                                                             |

| Sensor/Actuator power supply                               | Max. 12 W <sup>1)</sup>                                                                                                |

| Sensor/Actuator power supply                               | 1/0 nowor supply minus voltage drep for short signify protection                                                       |

| Voltage Voltage drop for short-circuit protection at 0.5 A | I/O power supply minus voltage drop for short-circuit protection                                                       |

|                                                            | Max. 2 VDC                                                                                                             |

| Summation current Short-circuit proof                      | Max. 0.5 A<br>Yes                                                                                                      |

| Digital inputs                                             | IC0                                                                                                                    |

| Quantity                                                   | Up to 4 if the 2 digital channels are used as digital inputs                                                           |

| Nominal voltage                                            |                                                                                                                        |

| Input characteristics per EN 61131-2                       | Type 1                                                                                                                 |

| Input voltage                                              | 18 to 30 VDC                                                                                                           |

| Input current at 24 VDC                                    | Typ. 3.5 mA                                                                                                            |

| Input circuit                                              | Sink                                                                                                                   |

| Input filter                                               | Unit                                                                                                                   |

| Hardware                                                   | ≤100 µs                                                                                                                |

| Software                                                   | Default 0 ms, configurable between 0 and 25 ms in 0.2 ms intervals                                                     |

|                                                            | -                                                                                                                      |

| Input resistance                                           | Τγρ. 6.67 kΩ                                                                                                           |

# Table 2: X67IF1121-1 - Technical data

| Order number                                                          | X67IF1121-1                                                                                                                                                                   |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Switching threshold                                                   |                                                                                                                                                                               |

| Low                                                                   | <5 V                                                                                                                                                                          |

| High                                                                  | >15 VDC                                                                                                                                                                       |

| Digital outputs                                                       |                                                                                                                                                                               |

| Quantity                                                              | Up to 2 if the 2 digital channels are used as digital outputs                                                                                                                 |

| Variant                                                               | Current-sourcing FET                                                                                                                                                          |

| Nominal voltage                                                       | 24 VDC                                                                                                                                                                        |

| Switching voltage                                                     | I/O power supply minus residual voltage                                                                                                                                       |

| Nominal output current                                                | 0.5 A                                                                                                                                                                         |

| Total nominal current                                                 | 1.6                                                                                                                                                                           |

|                                                                       |                                                                                                                                                                               |

| Output circuit                                                        | Source                                                                                                                                                                        |

| Output protection                                                     | Thermal shutdown in the event of overcurrent or short circuit, integrated protection<br>for switching inductive loads, reverse polarity protection of the output power supply |

| Diagnostic status                                                     | Output monitoring with 10 ms delay                                                                                                                                            |

| Leakage current when the output is switched off                       | <120 µA                                                                                                                                                                       |

| Peak short-circuit current                                            | <2.1 A                                                                                                                                                                        |

| Switch-on in the event of overload shutdown or short-circuit shutdown | Approx. 1 ms (depends on the module temperature)                                                                                                                              |

| Switching delay                                                       |                                                                                                                                                                               |

| $0 \rightarrow 1$                                                     | <100 µs                                                                                                                                                                       |

| $1 \rightarrow 0$                                                     | <150 µs                                                                                                                                                                       |

| Switching frequency                                                   |                                                                                                                                                                               |

| Resistive load                                                        | Max. 1000 Hz                                                                                                                                                                  |

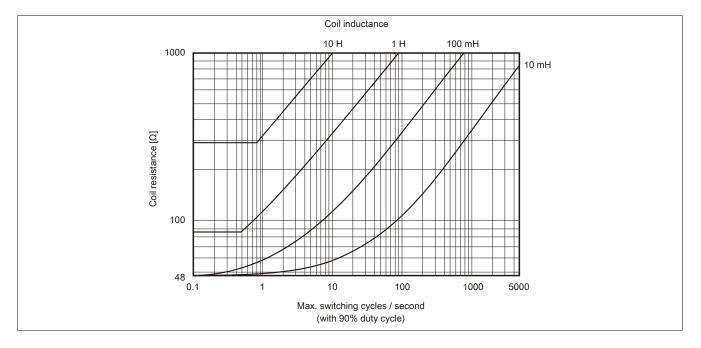

| Inductive load                                                        | See section "Switching inductive loads".                                                                                                                                      |

| Braking voltage when switching off inductive loads                    | Typ. 68 VDC                                                                                                                                                                   |

| Electrical properties                                                 | .,,,                                                                                                                                                                          |

| Electrical isolation                                                  | Bus isolated from channel and IF<br>Channel not isolated from channel and IF                                                                                                  |

| Operating conditions                                                  |                                                                                                                                                                               |

| Mounting orientation                                                  |                                                                                                                                                                               |

| Any                                                                   | Yes                                                                                                                                                                           |

| Installation elevation above sea level                                | 100                                                                                                                                                                           |

| 0 to 2000 m                                                           | No limitation                                                                                                                                                                 |

| >2000 m                                                               | Reduction of ambient temperature by 0.5°C per 100 m                                                                                                                           |

| Degree of protection per EN 60529                                     |                                                                                                                                                                               |

| Ambient conditions                                                    |                                                                                                                                                                               |

| Temperature                                                           |                                                                                                                                                                               |

| Operation                                                             | -25 to 60°C                                                                                                                                                                   |

| Derating                                                              | -2010/00/0                                                                                                                                                                    |

| Storage                                                               | -<br>-40 to 85°C                                                                                                                                                              |

| Transport                                                             | -40 to 85 °C                                                                                                                                                                  |

| Mechanical properties                                                 |                                                                                                                                                                               |

| Dimensions                                                            |                                                                                                                                                                               |

| Width                                                                 | 53 mm                                                                                                                                                                         |

|                                                                       |                                                                                                                                                                               |

| Height                                                                | 85 mm                                                                                                                                                                         |

| Depth                                                                 | 42 mm                                                                                                                                                                         |

| Weight                                                                | 195 g                                                                                                                                                                         |

| Torque for connections                                                | <b>H</b>                                                                                                                                                                      |

| M8                                                                    | Max. 0.4 Nm                                                                                                                                                                   |

| M12                                                                   | Max. 0.6 Nm                                                                                                                                                                   |

Table 2: X67IF1121-1 - Technical data

1) The power consumption of the sensors and actuators connected to the module is not permitted to exceed 12 W.

# 3.2 LED status indicators

| Figure                                         | LED            | Description                                              |                     |                                                                                      |  |  |

|------------------------------------------------|----------------|----------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------|--|--|

|                                                | Status indica- | Status indicator - X2X Link.                             |                     |                                                                                      |  |  |

|                                                | tor 1          | Green                                                    | Red                 | Description                                                                          |  |  |

|                                                |                | Off                                                      | Off                 | No power supply via X2X Link                                                         |  |  |

|                                                |                | On                                                       | Off                 | X2X Link supplied, communication OK                                                  |  |  |

|                                                |                | Off                                                      | On                  | X2X Link supplied but X2X Link communication not functioning                         |  |  |

|                                                |                | On                                                       | On                  | PREOPERATIONAL: X2X Link supplied, module not initialized                            |  |  |

| Status indicator 1:<br>Left: Green, Right: Red | 1              | Orange                                                   |                     | Lit when the module is receiving data via the RS232 interface.                       |  |  |

|                                                | 3              | Orange                                                   |                     | Lit when the module is receiving or transmitting data via the RS485/RS422 interface. |  |  |

|                                                | 2              | Status indicato                                          | or for input/output | t 3 and digital input 1.                                                             |  |  |

|                                                |                | LED                                                      |                     | Description                                                                          |  |  |

|                                                |                | Orange                                                   |                     | Input/output status of channel 3                                                     |  |  |

|                                                |                | Green                                                    |                     | Input status of channel 1                                                            |  |  |

|                                                |                | Orange and green <sup>1)</sup>                           |                     | Both channel 1 and channel 3 are active.                                             |  |  |

|                                                | 4              | Status indicator for input/output 4 and digital input 2. |                     |                                                                                      |  |  |

| 2 4                                            |                | LED                                                      |                     | Description                                                                          |  |  |

|                                                |                | Orange                                                   |                     | Input/output status of channel 4                                                     |  |  |

|                                                |                | Green                                                    |                     | Input status of channel 2                                                            |  |  |

|                                                |                | Orange and gr                                            |                     | Both channel 2 and channel 4 are active.                                             |  |  |

|                                                | Status indica- |                                                          | or for module fun   |                                                                                      |  |  |

|                                                | tor 2          | LED                                                      | Status              | Description                                                                          |  |  |

| Status indicator 2:                            |                | Green                                                    | Off                 | No power to module                                                                   |  |  |

| Left: Green, Right: Red                        |                |                                                          | Single flash        | RESET mode                                                                           |  |  |

|                                                |                |                                                          | Blinking            | PREOPERATIONAL mode                                                                  |  |  |

|                                                |                |                                                          | On                  | RUN mode                                                                             |  |  |

|                                                |                | Red                                                      | Off                 | No power to module or everything OK                                                  |  |  |

|                                                |                |                                                          | On                  | Error or reset status                                                                |  |  |

|                                                |                |                                                          | Single flash        | Warning/Error on an I/O channel. Level monitoring for digital out-                   |  |  |

|                                                |                |                                                          |                     | puts has been triggered.                                                             |  |  |

|                                                |                |                                                          | Double flash        | Supply voltage not in the valid range                                                |  |  |

1) Both LEDs are lit, but a mixed color is seen because there is only one light conductor.

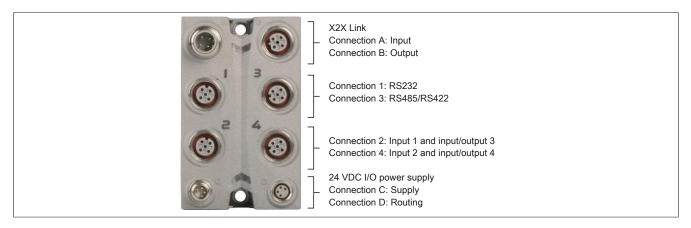

# **3.3 Connection elements**

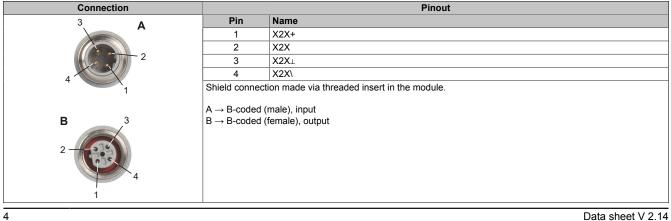

# 3.4 X2X Link

This module is connected to X2X Link using pre-assembled cables. The connection is made using M12 circular connectors.

# 3.5 24 VDC I/O power supply

The I/O power supply is connected via M8 connectors C and D. The I/O power supply is connected via connector C (male). Connector D (female) is used to route the I/O power supply to other modules.

# Information:

# The maximum permissible current for the I/O power supply is 8 A (4 A per connection pin)!

| Connection     |     | Pinout                                                                                             |

|----------------|-----|----------------------------------------------------------------------------------------------------|

| <sup>2</sup> C | Pin | Name                                                                                               |

| 1              | 1   | 24 VDC                                                                                             |

| 4              | 2   | 24 VDC                                                                                             |

|                | 3   | GND                                                                                                |

|                | 4   | GND                                                                                                |

|                |     | or (male) in module, feed for I/O power supply<br>or (female) in module, relay of I/O power supply |

# 3.6 Pinout

X67CA0A41.xxxx: M12 sensor cable, straight X67CA0A51.xxxx: M12 sensor cable, angled

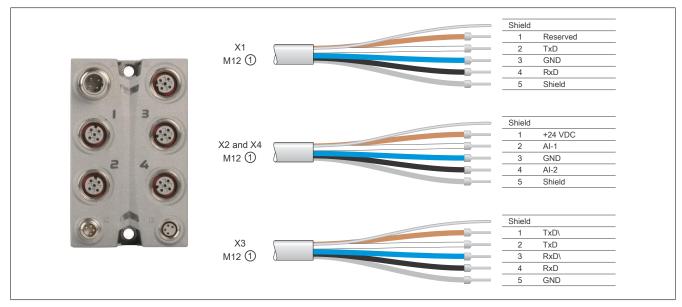

# 3.6.1 RS232 interface

The input is connected using M12 circular connectors.

| Connection |                           | Pinout                                     |

|------------|---------------------------|--------------------------------------------|

| X1         | Pin                       | Name                                       |

|            | 1                         | Reserved                                   |

| 1          | 2                         | TxD                                        |

| 2          | 3                         | GND                                        |

| 5          | 4                         | RxD                                        |

| 23         | 5                         | Shield                                     |

| 4          | Shield connect            | ion made via threaded insert in the module |

| 3          | $X1 \rightarrow A$ -keyed | (female), output                           |

# 3.6.2 RS485/RS422 interface

The input is connected using M12 circular connectors.

| Connection | Pinout                    |                                            |          |  |

|------------|---------------------------|--------------------------------------------|----------|--|

| X3         | Pin                       | RS422                                      | RS485    |  |

|            | 1                         | TxD\                                       | Reserved |  |

| 3          | 2                         | TxD                                        | Reserved |  |

| 2          | 3                         | RxD\                                       | Data\    |  |

|            | 4                         | RxD                                        | Data     |  |

|            | 5                         | GND                                        | GND      |  |

| 4          | Shield connecti           | ion made via threaded insert in the module |          |  |

| 1 5        |                           |                                            |          |  |

| 5          | $X3 \rightarrow A$ -keyed | (female), output                           |          |  |

# 3.6.3 Connections X2 and X4

| M12, 5-pin     |                                                        | Pinout                                                                                               |

|----------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Connection 2   | Pin                                                    | Name                                                                                                 |

| 1              | 1                                                      | 24 VDC sensor/actuator supply <sup>1)</sup>                                                          |

| 2              | 2                                                      | DI 1 or 2                                                                                            |

| 5.             | 3                                                      | GND                                                                                                  |

|                | 4                                                      | DI/DO 3 or 4                                                                                         |

|                | 5                                                      | Shield <sup>2)</sup>                                                                                 |

| 4 3            | <ol> <li>Sensors/Act</li> <li>Shielding als</li> </ol> | uators are not permitted to be supplied externally.<br>so provided by threaded insert in the module. |

| 2 3 4<br>1 5 4 | $X2 \rightarrow A$ -keyed                              | (female), input/output                                                                               |

| Connection 4   |                                                        |                                                                                                      |

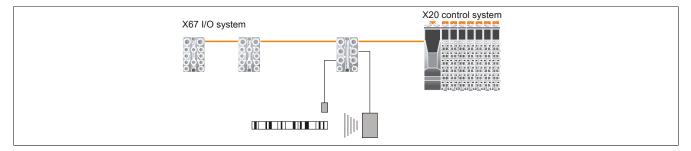

# 3.7 Usage example

In the application displayed here, the proximity sensor and barcode reader are connected with the communication module. The sensor activates the barcode scanner when a corresponding product arrives in the read area.

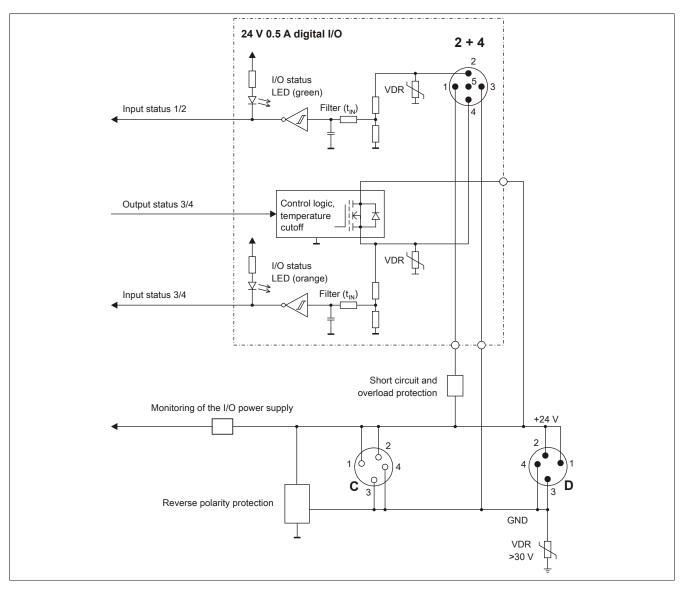

# 3.8 Input/Output circuit diagram

3.9 Switching inductive loads

# 4 Register description

# 4.1 General data points

In addition to the registers described in the register description, the module has additional general data points. These are not module-specific but contain general information such as serial number and hardware variant.

General data points are described in section "Additional information - General data points" in the X67 system user's manual.

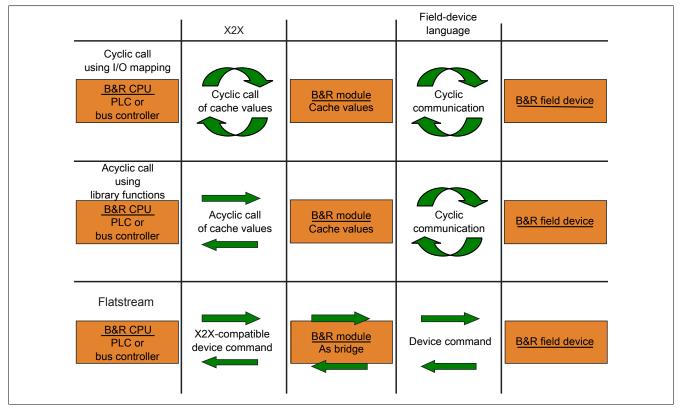

# 4.2 Function model 2 - Stream and Function model 254 - Cyclic stream

Function models "Stream" and "Cyclic stream" use a module-specific driver for the operating system. The interface can be controlled using library "DvFrame" and reconfigured at runtime.

### Function model - Stream

In function model "Stream", the CPU communicates with the module acyclically. The interface is relatively convenient, but the timing is very imprecise.

### Function model - Cyclic stream

Function model "Cyclic stream" was implemented later. From the application's point of view, there is no difference between function models "Stream" and "Cyclic stream". Internally, however, the cyclic I/O registers are used to ensure that communication follows deterministic timing.

# Information:

- In order to use function models "Stream" and "Cyclic stream", you must be using B&R controllers of type "SG4".

- These function models can only be used in X2X Link and POWERLINK networks.

| Register     | Name                                 | Data type | Read   |         | Write  |         |

|--------------|--------------------------------------|-----------|--------|---------|--------|---------|

|              |                                      |           | Cyclic | Acyclic | Cyclic | Acyclic |

| Module - Cor | ifiguration                          | · · · ·   |        |         |        |         |

| -            | AsynSize                             | -         |        |         |        |         |

| Configuratio | n                                    |           |        |         |        |         |

| 1294         | InputFilter                          | UINT      |        |         |        | •       |

| 1281         | OutputEnable                         | USINT     |        |         |        | •       |

| 6273         | CfO_ErrorID0007                      | USINT     |        |         |        | •       |

| Communicat   | ion                                  |           |        |         |        |         |

| 135          | Input state of digital inputs 1 to 4 | USINT     | •      |         |        |         |

|              | DigitalInput01                       | Bit 0     |        |         |        |         |

|              |                                      |           |        |         |        |         |

|              | DigitalInput04                       | Bit 3     |        |         |        |         |

| 129          | Output status of the digital outputs | USINT     |        |         | •      |         |

|              | DigitalOutput03                      | Bit 2     |        |         |        |         |

|              | DigitalOutput04                      | Bit 3     |        |         |        |         |

| 133          | Status of the digital outputs        | USINT     | •      |         |        |         |

|              | StatusDigitalOutput03                | Bit 2     |        |         |        |         |

|              | StatusDigitalOutput04                | Bit 3     |        |         |        |         |

| 137          | Status of the operating limits       | USINT     |        | •       |        |         |

|              | StatusSupplyVoltage                  | Bit 0     |        |         |        |         |

# 4.3 Function model 254 - Flatstream

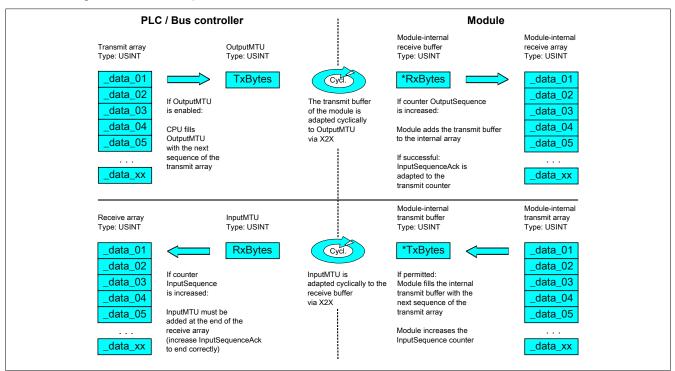

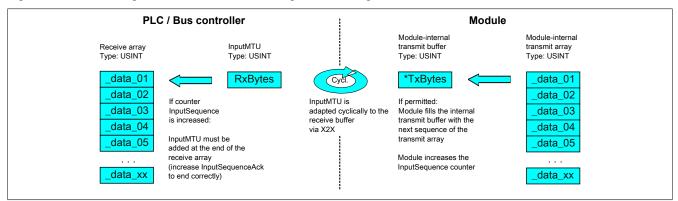

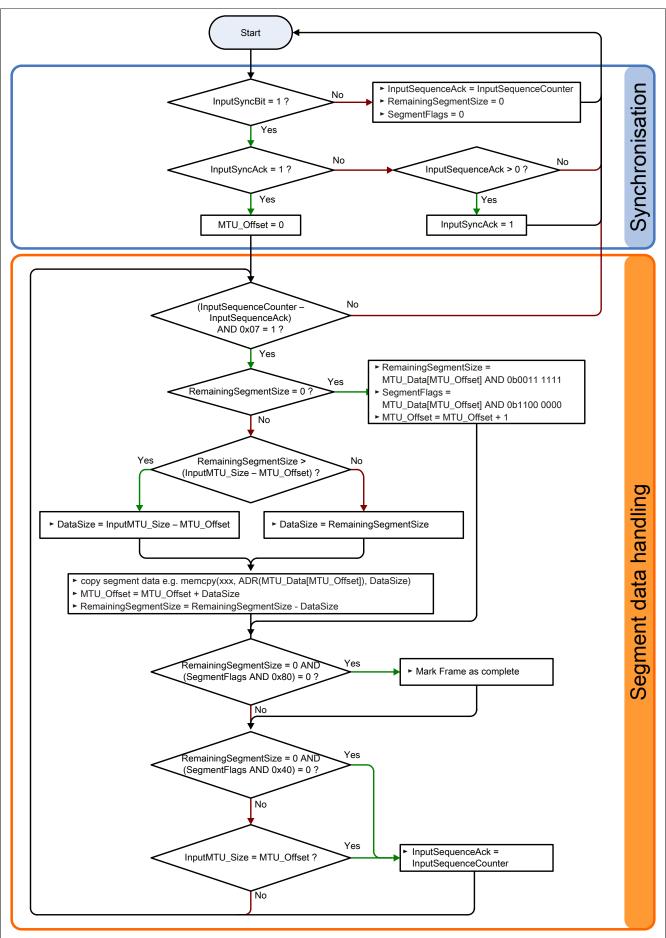

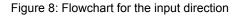

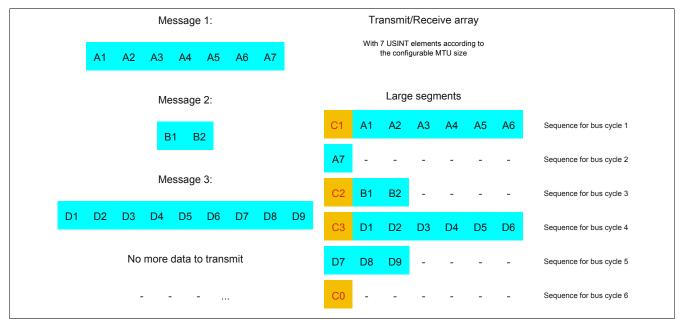

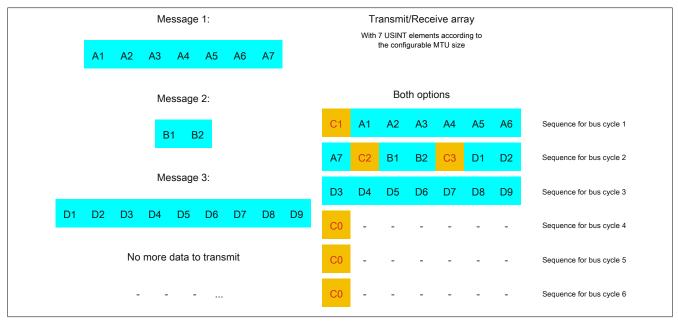

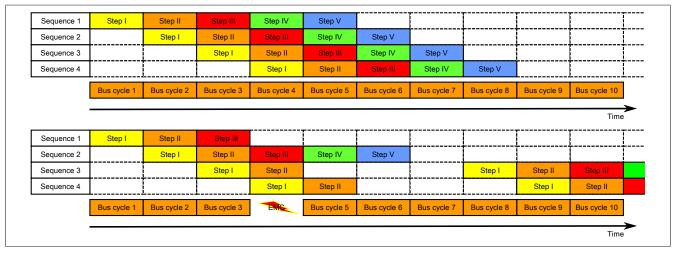

Flatstream provides independent communication between an X2X Link master and the module. This interface was implemented as a separate function model for the module. Serial information is transferred via cyclic input and output registers. The sequence and control bytes are used to control the data stream (see "Flatstream communication" on page 21).

When using function model Flatstream, the user can choose whether to use library "AsFItGen" in AS for implementation or to adapt Flatstream handling directly to the individual requirements of the application.

| Register      | Name                                      | Data type      | Read     |         | N      | /rite   |

|---------------|-------------------------------------------|----------------|----------|---------|--------|---------|

|               |                                           |                | Cyclic   | Acyclic | Cyclic | Acyclic |

| Configuration | - I/O and status                          |                | <b>*</b> |         |        |         |

| 1294          | InputFilter                               | UINT           |          |         |        | •       |

| 1281          | OutputEnable                              | USINT          |          |         |        | •       |

| 6273          | CfO ErrorID0007                           | USINT          |          |         |        | •       |

| Configuration |                                           |                |          |         |        |         |

| 260           | IF1CfgPhy                                 | UDINT          |          |         |        | •       |

| 772           | IF2CfgPhy                                 | UDINT          |          |         |        | •       |

| 268           | IF1phyBaud                                | UDINT          |          |         |        | •       |

| 780           | IF2phyBaud                                | UDINT          |          |         |        | •       |

|               | - Handshake                               | ODINI          |          |         |        |         |

| 284           | IF1hshCfg                                 | UDINT          |          |         |        | •       |

| 796           |                                           | UDINT          |          |         |        |         |

|               | IF2hshCfg                                 |                |          |         |        | •       |

| 292           | IF1hssXOnOff                              | UDINT          |          |         |        | •       |

| 804           | IF2hssXOnOff                              | UDINT          |          |         |        | •       |

| 298           | IF1hssPeriod                              | UINT           |          |         |        | •       |

| 810           | IF2hssPeriod                              | UINT           |          |         |        | •       |

| 274           | IF1hshInvTxF                              | UINT           |          |         |        | •       |

| 786           | IF2hshInvTxF                              | UINT           |          |         |        | •       |

| 324           | IF1rxILockUnlock                          | UDINT          |          |         |        | •       |

| 836           | IF2rxILockUnlock                          | UDINT          |          |         |        | •       |

| Configuration |                                           |                |          |         |        |         |

| 332           | IF1rxCtoEomSize                           | UDINT          |          |         |        | •       |

| 844           | IF2rxCtoEomSize                           | UDINT          |          |         |        | •       |

| 364           | IF1txCtoEomSize                           | UDINT          |          |         |        | •       |

| 876           | IF2txCtoEomSize                           | UDINT          |          |         |        | •       |

| 340           | IF1rxEomChar01                            | UDINT          |          |         |        | •       |

| 852           | IF2rxEomChar01                            | UDINT          |          |         |        | •       |

| 348           | IF1rxEomChar23                            | UDINT          |          |         |        | •       |

| 860           | IF2rxEomChar23                            | UDINT          |          |         |        | •       |

| 372           | IF1txEomChar01                            | UDINT          |          |         |        | •       |

| 884           | IF2txEomChar01                            | UDINT          |          |         |        | •       |

| 380           | IF1txEomChar23                            | UDINT          |          |         |        |         |

| 892           | IF2txEomChar23                            | UDINT          |          |         |        | •       |

| Communicatio  | 1                                         | ODINI          |          |         |        | •       |

| 135           | 1                                         | LICINT         | -        |         |        | 1       |

| 135           | Input state of digital inputs 1 to 4      | USINT          | •        |         |        |         |

|               | DigitalInput01                            | Bit 0          |          |         |        |         |

|               |                                           |                |          |         |        |         |

|               | DigitalInput04                            | Bit 3          |          |         |        |         |

| 129           | Output status of the digital outputs      | USINT          |          |         | •      |         |

|               | DigitalOutput03                           | Bit 2          |          |         |        |         |

|               | DigitalOutput04                           | Bit 3          |          |         |        |         |

| 6145          | Error message status bits                 | USINT          | •        |         |        |         |

|               | IF1StartBitError                          | Bit 0          |          |         |        |         |

|               | IF1StopBitError                           | Bit 1          |          |         |        |         |

|               | IF1ParityError                            | Bit 2          |          |         |        |         |

|               | IF1RXoverrun                              | Bit 3          |          |         |        |         |

|               | IF2StartBitError                          | Bit 4          |          |         |        |         |

|               | IF2StopBitError                           | Bit 5          |          |         |        |         |

|               | IF2ParityError                            | Bit 6          |          |         |        |         |

|               | IF2RXoverrun                              | Bit 7          |          |         |        |         |

| 6209          | Acknowledging the status bits             | USINT          |          |         | •      |         |

|               | IF1QuitStartBitError                      | Bit 0          |          |         |        |         |

|               | IF1QuitStopBitError                       | Bit 0          |          |         |        |         |

|               | IF1QuitParityError                        | Bit 1<br>Bit 2 |          |         |        |         |

|               | IF1QuitRXoverrun                          | Bit 3          |          |         |        |         |

|               | IF IQuitRXoverrun<br>IF2QuitStartBitError | Bit 3<br>Bit 4 |          |         |        |         |

|               |                                           |                |          |         |        |         |

|               | IF2QuitStopBitError                       | Bit 5          |          |         |        |         |

|               | IF2QuitParityError                        | Bit 6          |          |         |        |         |

|               | IF2QuitRXoverrun                          | Bit 7          |          |         |        |         |

| 133           | Status of the digital outputs             | USINT          | •        |         |        |         |

|               | StatusDigitalOutput03                     | Bit 2          |          |         |        |         |

|               | StatusDigitalOutput04                     | Bit 3          |          | 1       |        | 1       |

# X67IF1121-1

| Register                 | Name                           | Data type                             | Read   |         | W      | rite    |

|--------------------------|--------------------------------|---------------------------------------|--------|---------|--------|---------|

|                          |                                |                                       | Cyclic | Acyclic | Cyclic | Acyclic |

| 137                      | Status of the operating limits | USINT                                 | •      |         |        |         |

|                          | StatusSupplyVoltage            | Bit 0                                 |        |         |        |         |

| -latstream <sup>1)</sup> |                                | · · · · · · · · · · · · · · · · · · · |        |         |        |         |

| 196                      | IF1CfgMTU                      | UDINT                                 |        |         |        | •       |

| 212                      | IF2CfgMTU                      | UDINT                                 |        |         |        | •       |

| 204                      | IF1forwardDelay                | UINT                                  |        |         |        | •       |

| 220                      | IF2forwardDelay                | UINT                                  |        |         |        | •       |

| 0                        | IF1InputSequence               | USINT                                 | •      |         |        |         |

| 64                       | IF2InputSequence               | USINT                                 | •      |         |        |         |

| N                        | IF1RxByteN (index N = 1 to 27) | USINT                                 | •      |         |        |         |

| 64 + N                   | IF2RxByteN (index N = 1 to 27) | USINT                                 | •      |         |        |         |

| 32                       | IF1OutputSequence              | USINT                                 |        |         | •      |         |

| 96                       | IF2OutputSequence              | USINT                                 |        |         | •      |         |

| 32 + N                   | IF1TxByteN (index N = 1 to 27) | USINT                                 |        |         | •      |         |

| 96 + N                   | IF2TxByteN (index N = 1 to 27) | USINT                                 |        |         | •      |         |

1) A separate Flatstream is available for each interface.

# 4.4 Function model 254 - Bus controller

Function model "Bus controller" is a reduced form of function model "Flatstream". Instead of up to 27 Tx / Rx bytes, a maximum of 7 Tx / Rx bytes can be used.

# Information:

# It is not possible to change or expand the predefined configuration in this function model!

| Register      | Offset <sup>1)</sup> | Name                                 | Data type | Re     | ead     | Write  |         |

|---------------|----------------------|--------------------------------------|-----------|--------|---------|--------|---------|

|               |                      |                                      |           | Cyclic | Acyclic | Cyclic | Acyclic |

| Configuration | - I/O and state      | us                                   |           |        |         |        |         |

| 1294          | -                    | InputFilter                          | UINT      |        |         |        | •       |

| 1281          | -                    | OutputEnable                         | USINT     |        |         |        | •       |

| 6273          | -                    | CfO_ErrorID0007                      | USINT     |        |         |        | •       |

| onfiguration  | - Interface          |                                      |           |        |         |        |         |

| 260           | -                    | IF1CfgPhy                            | UDINT     |        |         |        | •       |

| 772           | -                    | IF2CfgPhy                            | UDINT     |        |         |        | •       |

| 268           | -                    | IF1phyBaud                           | UDINT     |        |         |        | •       |

| 780           | -                    | IF2phyBaud                           | UDINT     |        |         |        | •       |

| onfiguration  | - Handshake          |                                      |           |        |         |        |         |

| 284           | -                    | IF1hshCfg                            | UDINT     |        |         |        | •       |

| 796           | -                    | IF2hshCfg                            | UDINT     |        |         |        | •       |

| 292           | -                    | IF1hssXOnOff                         | UDINT     |        |         |        | •       |

| 804           | -                    | IF2hssXOnOff                         | UDINT     |        |         |        | •       |

| 298           | -                    | IF1hssPeriod                         | UINT      |        |         |        | •       |

| 810           | -                    | IF2hssPeriod                         | UINT      |        |         |        | •       |

| 274           | -                    | IF1hshInvTxF                         | UINT      |        |         |        | •       |

| 786           | -                    | IF2hshInvTxF                         | UINT      |        |         |        | •       |

| 324           | -                    | IF1rxILockUnlock                     | UDINT     |        |         |        | •       |

| 836           | -                    | IF2rxILockUnlock                     | UDINT     |        |         |        | •       |

| Configuration | - Frame              |                                      |           |        |         |        |         |

| 332           | -                    | IF1rxCtoEomSize                      | UDINT     |        |         |        | •       |

| 844           | -                    | IF2rxCtoEomSize                      | UDINT     |        |         |        | •       |

| 364           | -                    | IF1txCtoEomSize                      | UDINT     |        |         |        | •       |

| 876           | -                    | IF2txCtoEomSize                      | UDINT     |        |         |        | •       |

| 340           | -                    | IF1rxEomChar01                       | UDINT     |        |         |        | •       |

| 852           | -                    | IF2rxEomChar01                       | UDINT     |        |         |        | •       |

| 348           | -                    | IF1rxEomChar23                       | UDINT     |        |         |        | •       |

| 860           | -                    | IF2rxEomChar23                       | UDINT     |        |         |        | •       |

| 372           | -                    | IF1txEomChar01                       | UDINT     |        |         |        | •       |

| 884           | -                    | IF2txEomChar01                       | UDINT     |        |         |        | •       |

| 380           | -                    | IF1txEomChar23                       | UDINT     |        |         |        | •       |

| 892           | -                    | IF2txEomChar23                       | UDINT     |        |         |        | •       |

| communicatio  | n                    |                                      |           |        |         |        |         |

| 135           | 18                   | Input state of digital inputs 1 to 4 | USINT     | •      |         |        |         |

|               |                      | DigitalInput01                       | Bit 0     |        |         |        |         |

|               |                      |                                      |           |        |         |        |         |

|               |                      | DigitalInput04                       | Bit 3     |        |         |        |         |

| 129           | 18                   | Output status of the digital outputs | USINT     |        |         | ٠      |         |

|               |                      | DigitalOutput03                      | Bit 2     |        |         |        | 1       |

|               |                      | DigitalOutput04                      | Bit 3     |        |         |        | 1       |

| Register               | Offset <sup>1)</sup> | Name                           | Data type | R      | ad      | W      | rite    |

|------------------------|----------------------|--------------------------------|-----------|--------|---------|--------|---------|

| . tog.oto.             |                      |                                |           | Cyclic | Acyclic | Cyclic | Acyclic |

| 6145                   | 16                   | Error message status bits      | USINT     | •      |         |        |         |

|                        |                      | IF1StartBitError               | Bit 0     |        |         |        |         |

|                        |                      | IF1StopBitError                | Bit 1     |        |         |        |         |

|                        |                      | IF1ParityError                 | Bit 2     |        |         |        |         |

|                        |                      | IF1RXoverrun                   | Bit 3     |        |         |        |         |

|                        |                      | IF2StartBitError               | Bit 4     |        |         |        |         |

|                        |                      | IF2StopBitError                | Bit 5     |        |         |        |         |

|                        |                      | IF2ParityError                 | Bit 6     |        |         |        |         |

|                        |                      | IF2RXoverrun                   | Bit 7     |        |         |        |         |

| 6209                   | 16                   | Acknowledging the status bits  | USINT     |        |         | ٠      |         |

|                        |                      | IF1QuitStartBitError           | Bit 0     |        |         |        |         |

|                        |                      | IF1QuitStopBitError            | Bit 1     |        |         |        |         |

|                        |                      | IF1QuitParityError             | Bit 2     |        |         |        |         |

|                        |                      | IF1QuitRXoverrun               | Bit 3     |        |         |        |         |

|                        |                      | IF2QuitStartBitError           | Bit 4     |        |         |        |         |

|                        |                      | IF2QuitStopBitError            | Bit 5     |        |         |        |         |

|                        |                      | IF2QuitParityError             | Bit 6     |        |         |        |         |

|                        |                      | IF2QuitRXoverrun               | Bit 7     |        |         |        |         |

| 133                    | 19                   | Status of the digital outputs  | USINT     | •      |         |        |         |

|                        |                      | StatusDigitalOutput03          | Bit 2     |        |         |        |         |

|                        |                      | StatusDigitalOutput04          | Bit 3     |        |         |        |         |

| 137                    | -                    | Status of the operating limits | USINT     |        | •       |        |         |

|                        |                      | StatusSupplyVoltage            | Bit 0     |        |         |        |         |

| atstream <sup>2)</sup> |                      |                                |           |        |         |        |         |

| 196                    | -                    | IF1CfgMTU                      | UDINT     |        |         |        | •       |

| 212                    | -                    | IF2CfgMTU                      | UDINT     |        |         |        | •       |

| 204                    | -                    | IF1forwardDelay                | UINT      |        |         |        | •       |

| 220                    | -                    | IF2forwardDelay                | UINT      |        |         |        | •       |

| 0                      | 0                    | IF1InputSequence               | USINT     | ٠      |         |        |         |

| 64                     | 8                    | IF2InputSequence               | USINT     | •      |         |        |         |

| N                      | N                    | IF1RxByteN (index N = 1 to 7)  | USINT     | •      |         |        |         |

| 64 + N                 | 8 + N                | IF2RxByteN (index N = 1 to 7)  | USINT     | •      |         |        |         |

| 32                     | 0                    | IF1OutputSequence              | USINT     |        |         | ٠      |         |

| 96                     | 8                    | IF2OutputSequence              | USINT     |        |         | •      |         |

| 32 + N                 | N                    | IF1TxByteN (index N = 1 to 7)  | USINT     |        |         | ٠      |         |

| 96 + N                 | 8 + N                | IF2TxByteN (index N = 1 to 7)  | USINT     |        |         | •      |         |

The offset specifies the position of the register within the CAN object. A separate Flatstream is available for each interface. 1)

2)

#### 4.4.1 Using the module on the bus controller

Function model 254 "Bus controller" is used by default only by non-configurable bus controllers. All other bus controllers can use other registers and functions depending on the fieldbus used.

For detailed information, see section "Additional information - Using I/O modules on the bus controller" in the X67 user's manual (version 3.30 or later).

# 4.4.2 CAN I/O bus controller

The module occupies 3 analog logical slots with CAN I/O.

# 4.5 Configuration - I/O and status

# 4.5.1 Configuring the input filter

Name:

InputFilter

The filter value for all digital inputs can be configured in this register.

The filter value can be configured in steps of 100  $\mu$ s. It makes sense to enter values in steps of 2, however, since the input signals are sampled every 200  $\mu$ s.

| Data type | Values | Filter                                              |

|-----------|--------|-----------------------------------------------------|

| USINT     | 0      | No software filter (bus controller default setting) |

|           | 2      | 0.2 ms                                              |

|           |        |                                                     |

|           | 250    | 25 ms - Higher values are limited to this value.    |

# 4.5.2 Input/output configuration channels 3 and 4

Name:

OutputEnable

This register configures channels 3 and 4 as either an input or output.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

Bit structure:

| Bit   | Name       | Value | Information                                          |

|-------|------------|-------|------------------------------------------------------|

| 0 - 1 | Reserved   | -     |                                                      |

| 2     | Channel 03 | 0     | Configured as input (bus controller default setting) |

|       |            | 1     | Configured as output                                 |

| 3     | Channel 04 | 0     | Configured as input (bus controller default setting) |

|       |            | 1     | Configured as output                                 |

| 4 - 7 | Reserved   | -     |                                                      |

# 4.5.3 Forward error to the application

Name:

# CfO\_ErrorID0007

This register sets which error messages are forwarded to the application.

| Data type | Values                 | Bus controller default setting |

|-----------|------------------------|--------------------------------|

| USINT     | See the bit structure. | 0                              |

| Bit | Name                | Value | Information                                |

|-----|---------------------|-------|--------------------------------------------|

| 0   | StartBitError - IF1 | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate faulty start bit                  |

| 1   | StopBitError - IF1  | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate faulty stop bit                   |

| 2   | ParityError - IF1   | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate faulty parity bit                 |

| 3   | RXoverrun - IF1     | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate overflow in the receive direction |

| 4   | StartBitError - IF2 | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate faulty start bit                  |

| 5   | StopBitError - IF2  | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate faulty stop bit                   |

| 6   | ParityError - IF2   | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate faulty parity bit                 |

| 7   | RXoverrun - IF2     | 0     | Ignore (bus controller default setting)    |

|     |                     | 1     | Indicate overflow in the receive direction |

# 4.6 Configuration - Serial interface

# 4.6.1 Configuration - Interfaces

Name:

IF1CfgPhy to IF2CfgPhy

These registers are used to configure the interfaces. Only the corresponding interface values are permitted to be used for each register.

- IF1CfgPhy configures RS232 interface

- IF2CfgPhy configures RS422/485 interface

After all other configuration registers have been written, the last write command must enable the interface. If parameters need to be changed, the interface must first be disabled.

| Data type | Values             | Bus controller default setting |

|-----------|--------------------|--------------------------------|

| UDINT     | See bit structure. | 0x80245                        |

#### Bit structure:

| Bit     | Description                            | Value | Information                                         |

|---------|----------------------------------------|-------|-----------------------------------------------------|

| 0 - 7   | Parity bit configuration <sup>1)</sup> | 48    | "0" - (low) bit is always 0                         |

|         |                                        | 49    | "1" - (high) bit is always 1                        |

|         |                                        | 69    | 1 stop bit (bus controller default setting)         |

|         |                                        | 78    | "N" - (no) no bit                                   |

|         |                                        | 79    | "O" - (odd) odd parity                              |

| 8 - 15  | Number of stop bits                    | 2     | 1 stop bit (bus controller default setting)         |

|         |                                        | 4     | 2 stop bits                                         |

| 16 - 23 | Number of data bits per character      | 7     | 7 data bits                                         |

|         |                                        | 8     | 8 data bits (bus controller default setting)        |

| 24 - 31 | Interface mode                         | 0     | Interface disabled (bus controller default setting) |

|         |                                        | 2     | RS232 interface active                              |

|         |                                        | 4     | RS422 interface active <sup>2)</sup>                |

|         |                                        | 5     | RS422 interface active as bus <sup>3)</sup>         |

|         |                                        | 6     | RS485 interface active with echo                    |

|         |                                        | 7     | RS485 interface active without echo                 |

1) ASCII-encoded decimal values

2) Connection between 2 stations

3) Connections between multiple stations possible. Transmit lines connected as with RS485 tri-state.

### 4.6.2 Setting the baud rate

Name:

IF1phyBaud to IF2phyBaud

This register sets the baud rate of the interface in bit/s.

| Data type | Value  | Function                                    |

|-----------|--------|---------------------------------------------|

| UDINT     | 1200   | 1.2 kbaud                                   |

|           | 2400   | 2.4 kbaud                                   |

|           | 4800   | 4.8 kbaud                                   |

|           | 9600   | 9.6 kbaud                                   |

|           | 19200  | 19.2 kbaud                                  |

|           | 38400  | 38.4 kbaud                                  |

|           | 57600  | 57.6 kbaud (bus controller default setting) |

|           | 115200 | 115.2 kbaud                                 |

# 4.7 Configuration - Handshake

In order to ensure serial communication runs smoothly, the size of the receive buffer being used in the module must be made known. In addition, the user can specify a software- or hardware-based handshake algorithm.

# 4.7.1 RTS evaluation and frame detection

### Name:

# IF1hshCfg to IF2hshCfg

This register configures how the hardware RTS handshake line is controlled depending on the fill level of the receive buffer in addition to generally enabling frame detection on the hardware side.

The RTS line is enabled as long as data is being sent. This Tx-Framing mode can be used to control external interface converters.

| Data type | Values             | Bus controller default setting |

|-----------|--------------------|--------------------------------|

| UDINT     | See bit structure. | 0                              |

#### Bit structure:

| Bit     | Description     | Value | Information                                                                                    |

|---------|-----------------|-------|------------------------------------------------------------------------------------------------|

| 0 - 7   | Frame detection | 0     | RTS line freely available for other flow control methods (bus con-<br>troller default setting) |

|         |                 | 16    | Tx frame detection switched on for RTS line                                                    |

|         |                 | 80    | Tx frame detection switched on for RTS line (without echo)                                     |

| 8 - 15  | Flow control    | 0     | RTS line freely available for other flow control methods (bus con-<br>troller default setting) |

|         |                 | 16    | RTS line controlled by the fill level of the receive buffer                                    |

| 16 - 31 | Reserved        | 0     |                                                                                                |

#### 4.7.2 Software handshake control characters

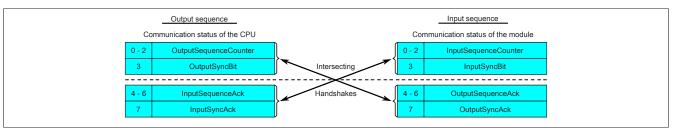

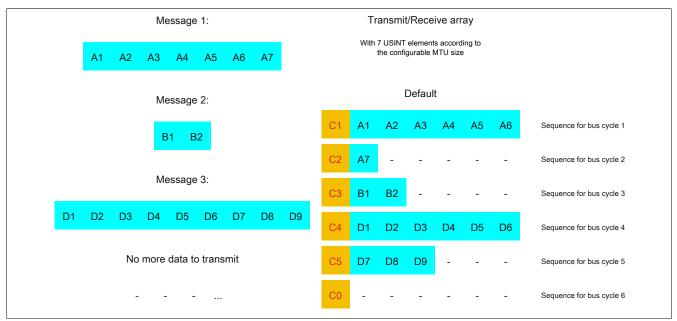

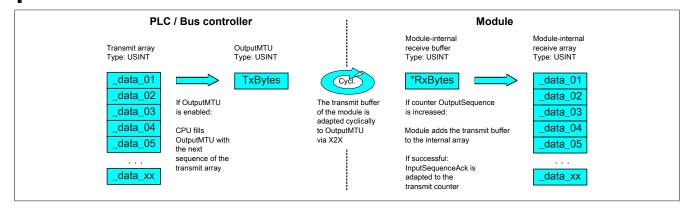

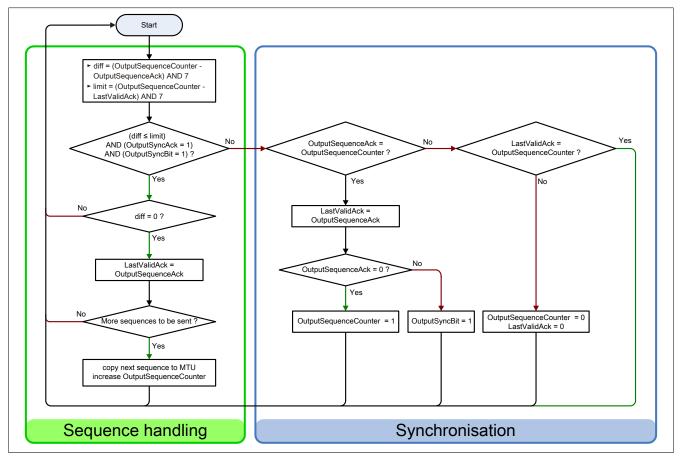

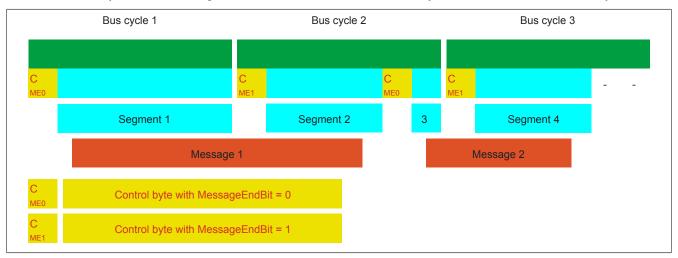

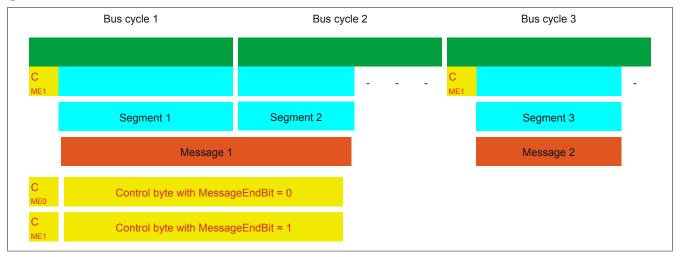

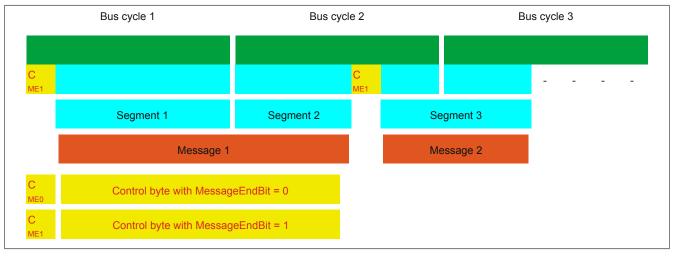

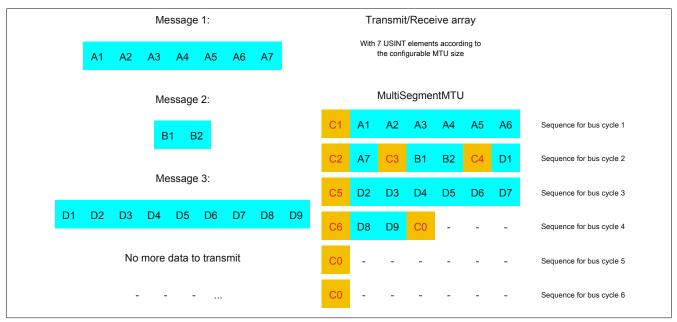

#### Name: